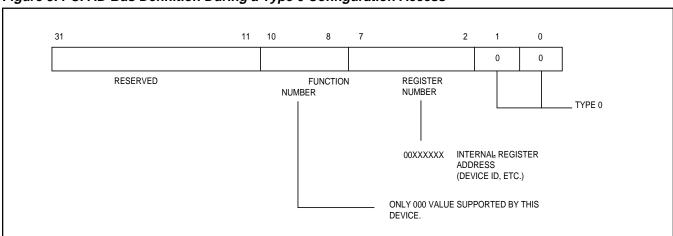

# S5935 PCI PRODUCT DATA BOOK

For Marketing and Application Information Contact:

Applied Micro Circuits Corporation 6290 Sequence Drive San Diego, CA 92121-4358 (800) 755-2622 (619) 450-9333 Fax (619) 450-9885 http://www.amcc.com The material in this document supersedes all previous documentation issued for any of the products included herein.

AMCC reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

AMCC reserves the right to ship devices of higher grade in place of those of lower grade.

AMCC SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

AMCC and Matchmaker are registereded trademarks of Applied Micro Circuits Corporation.

All other product names are trademarks, registered trademarks, or servicemarks of their respective owners.

# **C**ONTENTS

| 1. ARCHITECTURAL OVERVIEW                           | 1-1  |

|-----------------------------------------------------|------|

| Introduction to the PCI Local Bus                   | 1-1  |

| S5935 Architecture                                  | 1-2  |

| S5935 Register Architecture                         | 1-2  |

| PCI Configuration Registers                         | 1-2  |

| PCI Operation Registers                             | 1-3  |

| Add-On Bus Operation Registers                      | 1-3  |

| Non-Volatile Memory Interface                       | 1-3  |

| Mailbox Operation                                   | 1-4  |

| Pass-Thru Operation                                 | 1-5  |

| FIFO PCI Bus Mastering Operation                    | 1-5  |

| 2. SIGNAL DESCRIPTIONS                              | 2-9  |

| Signal Type Definition                              | 2-9  |

| Address and Data Pins – PCI Local Bus               | 2-10 |

| PCI Bus Interface Signals                           | 2-10 |

| System Pins – PCI Local Bus                         | 2-11 |

| Interface Control Pins – PCI Bus Signal             | 2-11 |

| Arbitration Pins (Bus Masters Only) – PCI Local Bus | 2-12 |

| Error Reporting Pins – PCI Local Bus                | 2-12 |

| Interrupt Pin – PCI Local Bus                       | 2-12 |

| Non-Volatile Memory Interface Signals               | 2-13 |

| Serial nv Devices                                   | 2-13 |

| Byte-Wide nv Devices                                | 2-13 |

| Add-On Bus Interface Signals                        | 2-14 |

| Register Access Pins                                | 2-14 |

| FIFO Access Pins                                    | 2-15 |

| Pass-Thru Interface Pins                            | 2-15 |

| System Pins                                         | 2-16 |

| 3. PCI CONFIGURATION REGISTERS                      | 3-17 |

| PCI Configuration Space Header                      | 3-18 |

| Vendor Identification Register (VID)                | 3-19 |

| Device Identification Register (DID)                | 3-20 |

| PCI Command Register (PCICMD)                       | 3-21 |

| PCI Status Register (PCISTS)                        | 3-23 |

| Revision Identification Register (RID)              | 3-25 |

| Class Code Register (CLCD)                          | 3-26 |

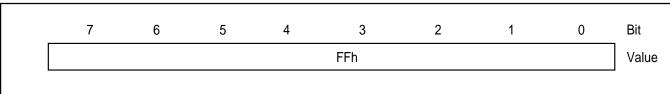

| Cache Line Size Register (CALN)                     | 3-30 |

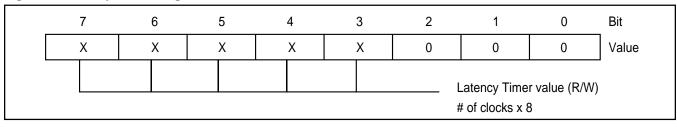

| Latency Timer Register (LAT)                        | 3-31 |

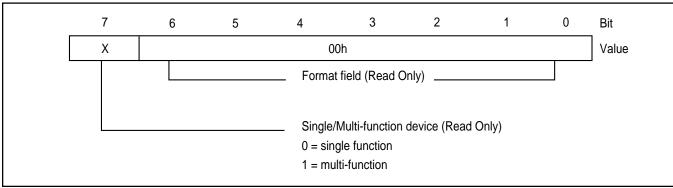

| Header Type Register (HDR)                          | 3-32 |

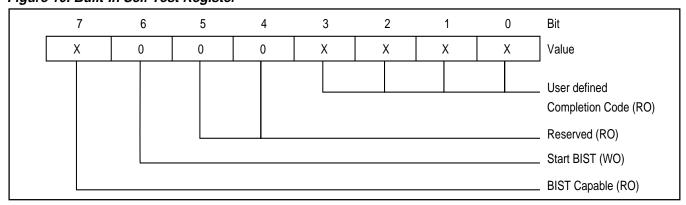

| Built-in Self-Test Register (BIST)                  | 3-33 |

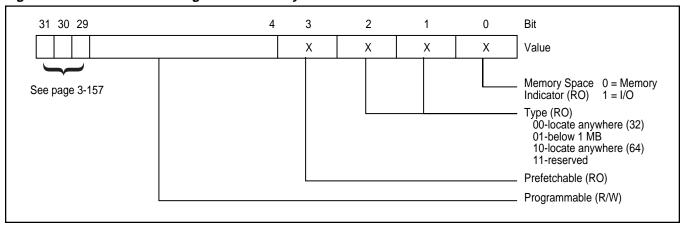

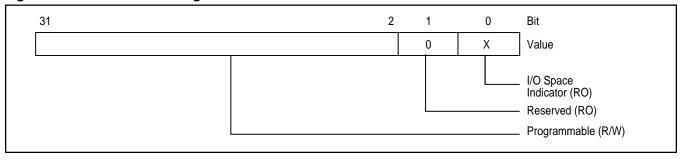

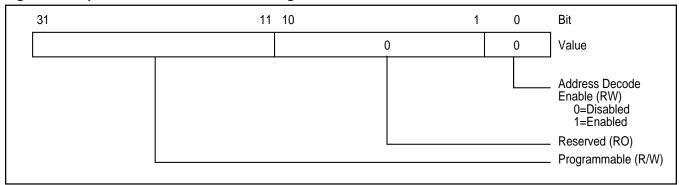

| Base Address Registers (BADR)                       |      |

| Expansion ROM Base Address Register (XROM)          | 3-38 |

| Interrupt Line Register (INTLN)                     |      |

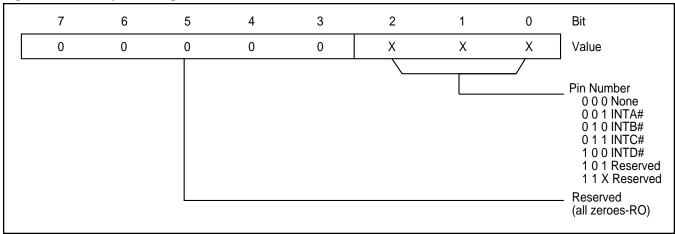

| Interrupt PIN Register (INTPIN)                     | 3-41 |

| 3-42 |

|------|

| 3-43 |

| 4-45 |

| 4-46 |

| 4-46 |

| 4-46 |

| 4-47 |

| 4-48 |

| 4-49 |

| 4-50 |

| 4-51 |

| 4-53 |

| 4-57 |

| 5-61 |

| 5-62 |

| 5-62 |

| 5-62 |

| 5-63 |

| 5-64 |

| 5-64 |

| 5-65 |

| 5-66 |

| 5-68 |

| 5-71 |

| 5-74 |

| 5-75 |

| 6-77 |

| 6-77 |

| 6-77 |

| 6-78 |

| 6-80 |

| 6-82 |

| 7-85 |

| 7-86 |

| 7-86 |

| 7-88 |

| 7-89 |

| 7-89 |

| 7-89 |

| 7-90 |

| 7-91 |

| 7-91 |

|      |

|    | Target Disconnects                                                    | 7-92           |

|----|-----------------------------------------------------------------------|----------------|

|    | Target Requested Retries                                              |                |

|    | Target Aborts                                                         |                |

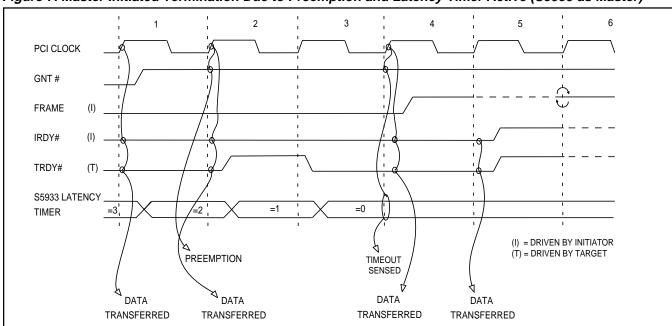

|    | PCI Bus Mastership                                                    | 7-95           |

|    | Bus Mastership Latency Components                                     |                |

|    | Bus Arbitration                                                       |                |

|    | Bus Acquisition                                                       |                |

|    | Target Latency                                                        |                |

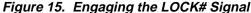

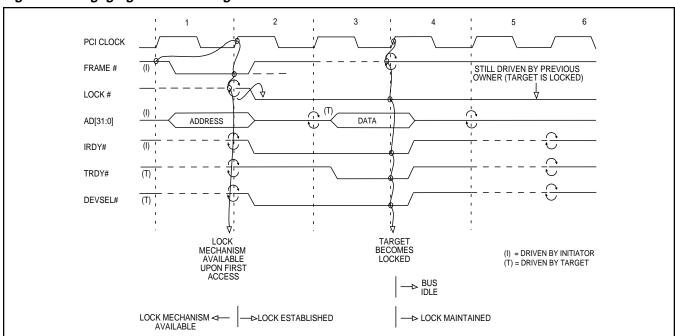

|    | Target Locking                                                        |                |

|    | PCI Bus Interrupts                                                    |                |

|    | PCI Bus Parity Errors                                                 |                |

|    |                                                                       |                |

| 8. | ADD-ON BUS INTERFACE                                                  | 8-99           |

|    | Add-On Operation Register Accesses                                    |                |

|    | Add-On Interface Signals                                              |                |

|    | System Signals                                                        |                |

|    | Register Access Signals                                               |                |

|    | Asynchronous Register Accesses                                        |                |

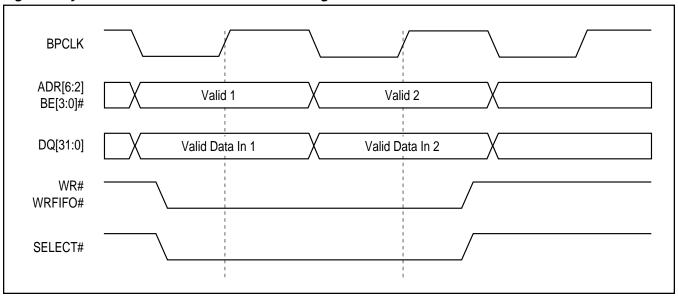

|    | Synchronous FIFO and Pass-Thru Data Register Accesses                 |                |

|    | nv Memory Accesses Through the Add-On General Control/Status Register |                |

|    | Mailbox Bus Interface                                                 |                |

|    | Mailbox Interrupts                                                    |                |

|    | FIFO Bus Interface                                                    |                |

|    | FIFO Direct Access Inputs                                             |                |

|    | FIFO Status Signals                                                   |                |

|    | FIFO Control Signals                                                  |                |

|    | Pass-Thru Bus Interface                                               |                |

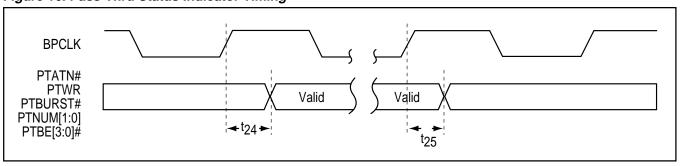

|    | Pass-Thru Status Indicators                                           |                |

|    | Pass-Thru Control Inputs                                              |                |

|    | Non-Volatile Memory Interface                                         |                |

|    | Non-Volatile Memory Interface Signals                                 |                |

|    | Accessing Non-Volatile Memory                                         |                |

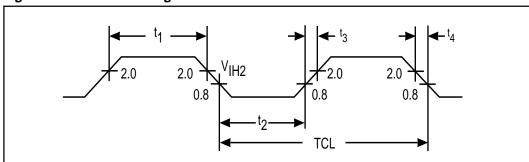

|    | nv Memory Device Timing Requirements                                  |                |

|    | The Mothery Boxios Tilling Roquitornonic                              |                |

| 9. | MAILBOX OVERVIEW                                                      | 9-109          |

|    | Functional Description                                                |                |

|    | Mailbox Empty/Full Conditions                                         |                |

|    | Mailbox Interrupts                                                    |                |

|    | Add-On Outgoing Mailbox 4, Byte 3 Access                              |                |

|    | Bus Interface                                                         |                |

|    | PCI Bus Interface                                                     |                |

|    | Add-On Bus Interface                                                  |                |

|    | 8-Bit and 16-Bit Add-On Interfaces                                    |                |

|    | Configuration                                                         |                |

|    | Mailbox Status                                                        |                |

|    | Mailbox Status                                                        | 9-112<br>9-113 |

|    |                                                                       |                |

| 10. FIFO OVERVIEW                                                    | 10-117 |

|----------------------------------------------------------------------|--------|

| Functional Description                                               | 10-117 |

| FIFO Buffer Management and Endian Conversion                         | 10-117 |

| FIFO Advance Conditions                                              | 10-117 |

| Endian Conversion                                                    | 10-118 |

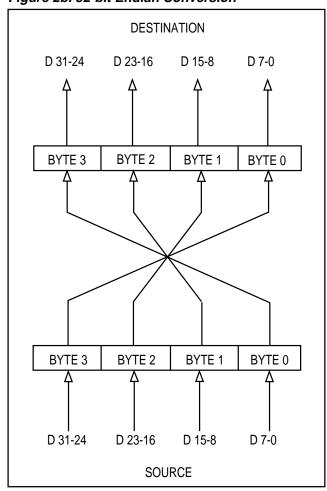

| 64-Bit Endian Conversion                                             | 10-119 |

| Add-On FIFO Status Indicators                                        | 10-120 |

| Add-On FIFO Control Signals                                          | 10-120 |

| PCI Bus Mastering with the FIFO                                      | 10-120 |

| Add-On Initiated Bus Mastering                                       | 10-120 |

| PCI Initiated Bus Mastering                                          | 10-121 |

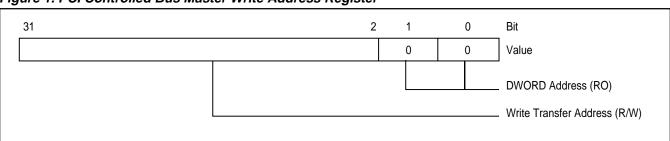

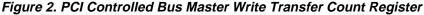

| Address and Transfer Count Registers                                 | 10-121 |

| Bus Mastering FIFO Management Schemes                                | 10-121 |

| FIFO Bus Master Cycle Priority                                       | 10-122 |

| FIFO Generated Bus Master Interrupts                                 | 10-122 |

| Bus Interface                                                        | 10-122 |

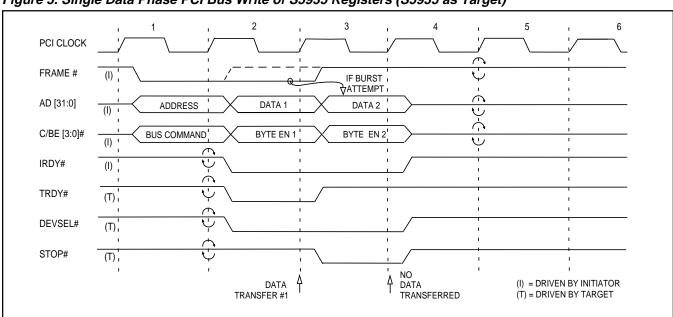

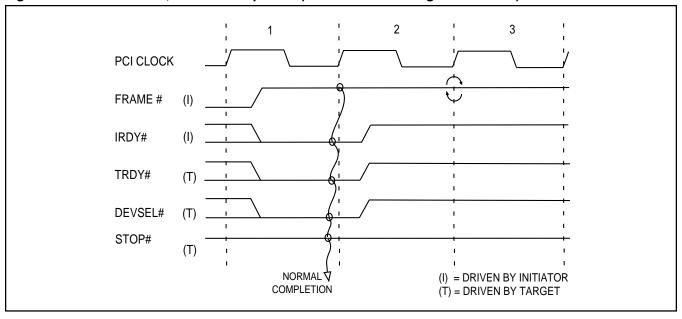

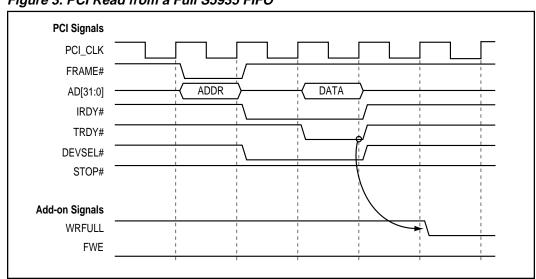

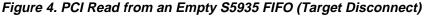

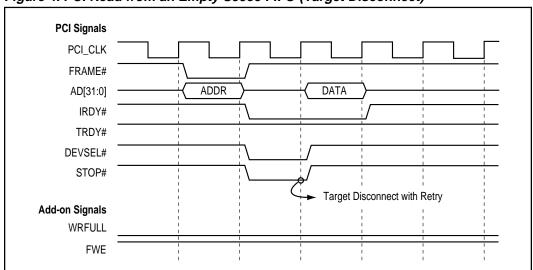

| FIFO PCI Interface (Target Mode)                                     | 10-122 |

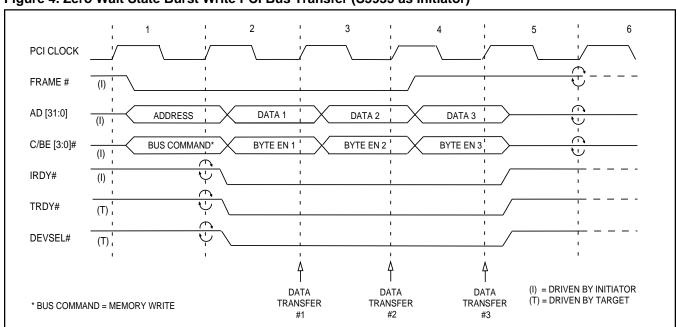

| FIFO PCI Interface (Initiator Mode)                                  | 10-123 |

| FIFO PCI Bus Master Reads                                            | 10-125 |

| FIFO PCI Bus Master Writes                                           | 10-125 |

| Add-On Bus Interface                                                 | 10-125 |

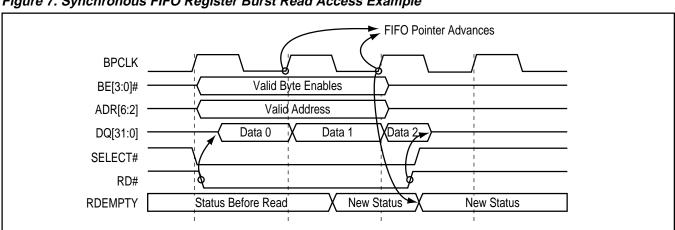

| Add-On FIFO Register Accesses                                        | 10-125 |

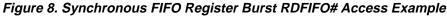

| Add-On FIFO Direct Access Mode                                       | 10-126 |

| Additional Status/Control Signals for Add-On Initiated Bus Mastering | 10-127 |

| FIFO Generated Add-On Interrupts                                     | 10-128 |

| 8-Bit and 16-Bit FIFO Add-On Interfaces                              | 10-128 |

| Configuration                                                        | 10-129 |

| FIFO Setup During Initialization                                     | 10-129 |

| FIFO Status and Control Bits                                         | 10-129 |

| PCI Initiated FIFO Bus Mastering Setup                               | 10-130 |

| Add-On Initiated FIFO Bus Mastering Setup                            | 10-131 |

| 11. PASS-THRU OVERVIEW                                               | 11-133 |

| Functional Description                                               | 11-133 |

| Pass-Thru Transfers                                                  | 11-133 |

| Pass-Thru Status/Control Signals                                     | 11-134 |

| Pass-Thru Add-On Data Bus Sizing                                     | 11-134 |

| Bus Interface                                                        | 11-134 |

| PCI Bus Interface                                                    | 11-134 |

| PCI Pass-Thru Single Cycle Accesses                                  | 11-134 |

| PCI Pass-Thru Burst Accesses                                         | 11-134 |

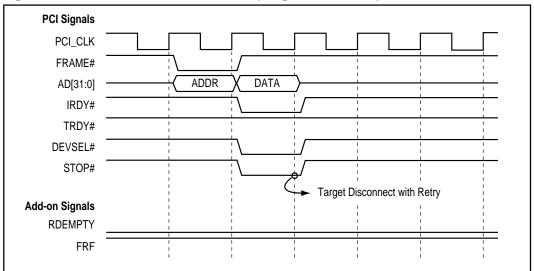

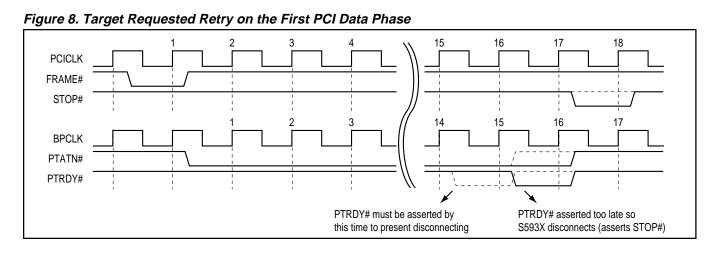

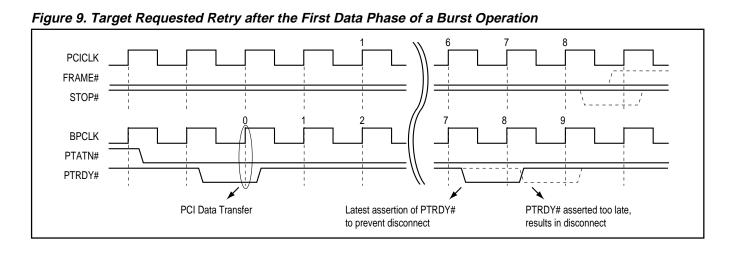

| PCI Retry Conditions                                                 | 11-134 |

| PCI Write Retries                                                    | 11-134 |

| PCI Read Retries                                                     | 11-136 |

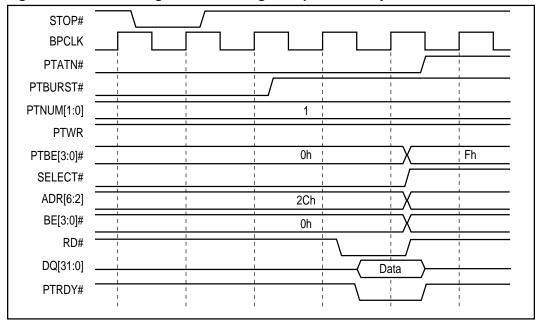

| Add-On Bus Interface                                                 | 11-136 |

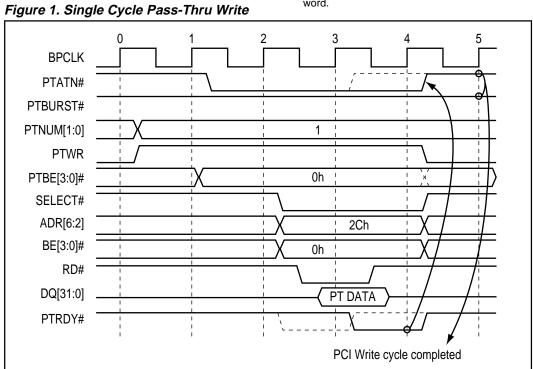

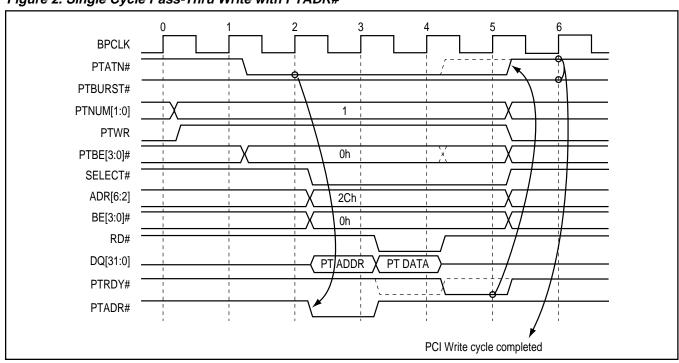

| Single Cycle Pass-Thru Writes                                        | 11-136 |

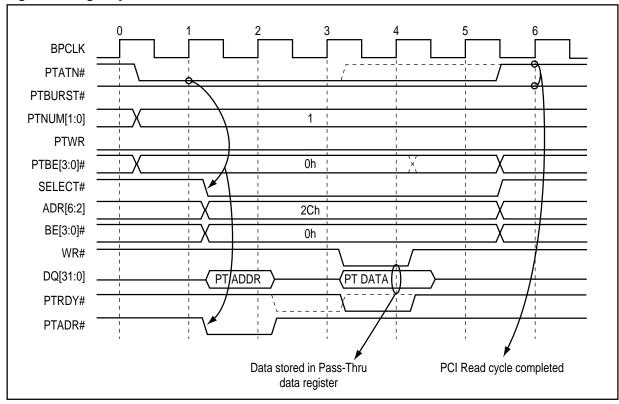

| Single Cycle Pass-Thru Reads                    | 11-138 |

|-------------------------------------------------|--------|

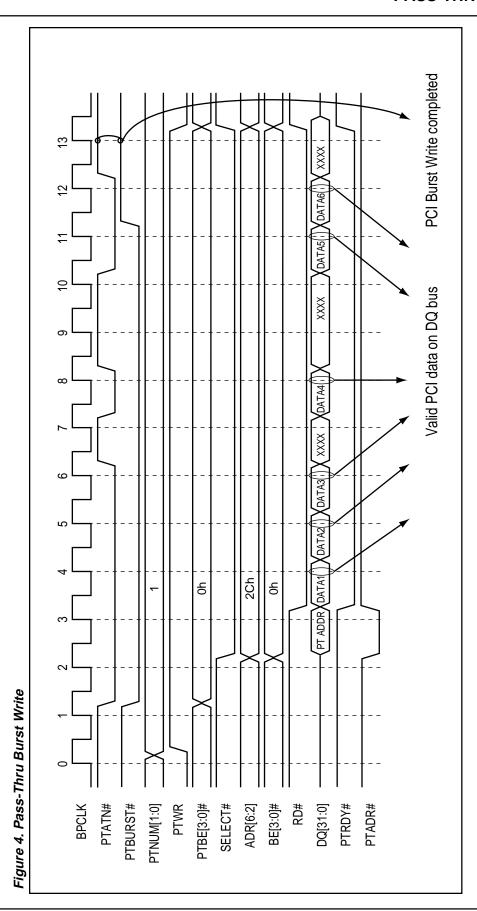

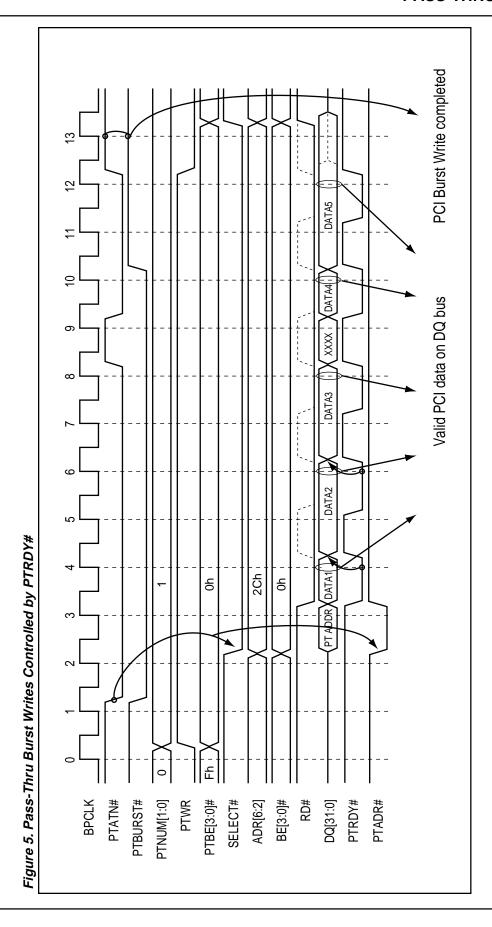

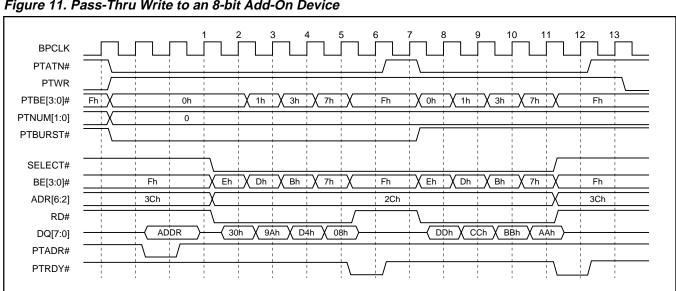

| Pass-Thru Burst Writes                          | 11-139 |

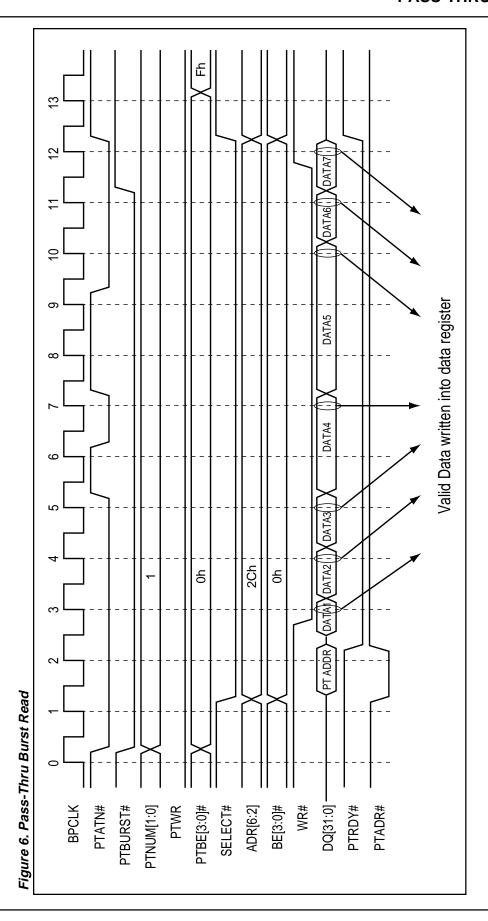

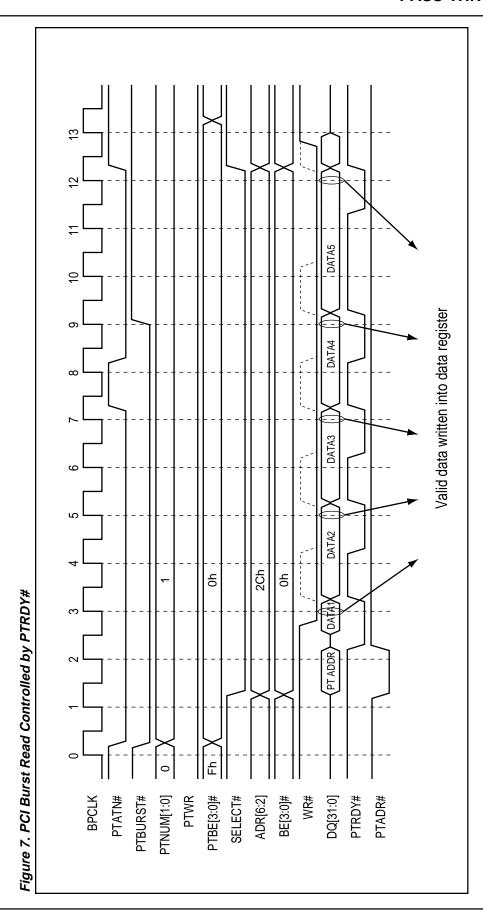

| Pass-Thru Burst Reads                           | 11-143 |

| Add-On Pass-Thru Disconnect Operation           | 11-147 |

| 8-Bit and 16-Bit Pass-Thru Add-On Bus Interface | 11-148 |

| Configuration                                   | 11-151 |

| S5935 Base Address Register Definition          | 11-151 |

| Creating a Pass-Thru Region                     | 11-151 |

| Accessing a Pass-Thru Region                    | 11-152 |

| 12. ELECTRICAL CHARACTERISTICS                  | 12-153 |

| Absolute Maximum Ratings                        | 12-153 |

| DC Characteristics                              | 12-153 |

| PCI Bus Signals                                 |        |

| Add-On Bus Signals                              | 12-155 |

| AC Characteristics                              |        |

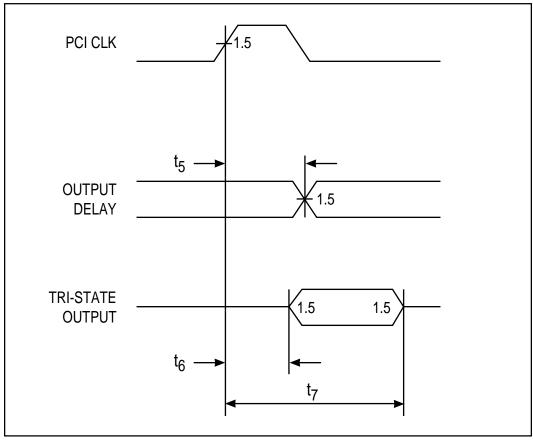

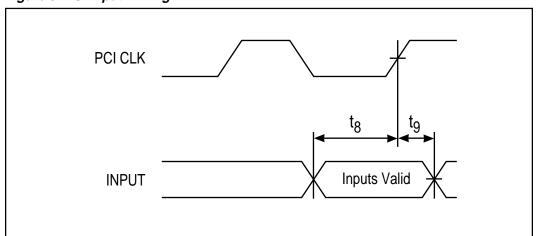

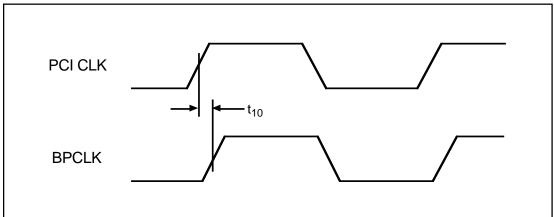

| PCI Bus Timings                                 | 12-156 |

| Add-On Bus Timings                              |        |

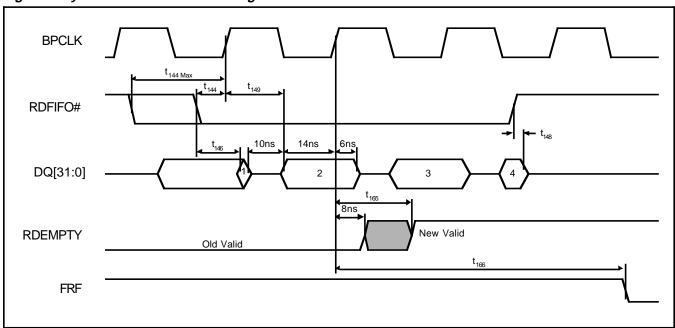

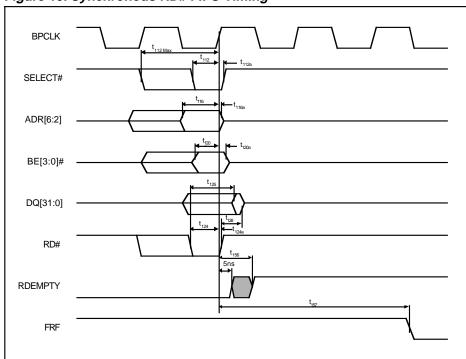

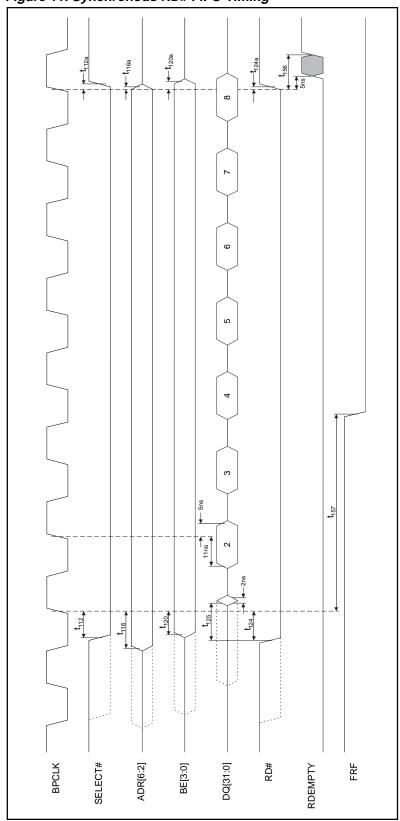

| Synchronous RDFIFO# Timing                      | 12-159 |

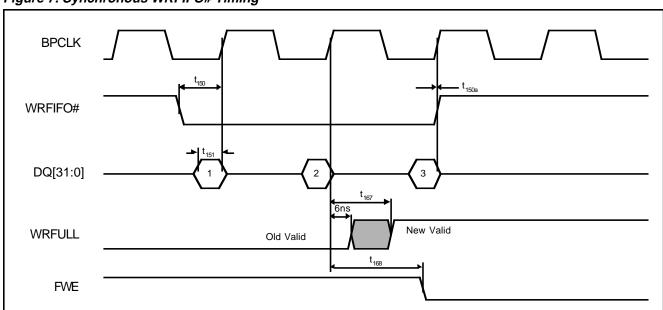

| Synchronous WRFIFO# Timing                      |        |

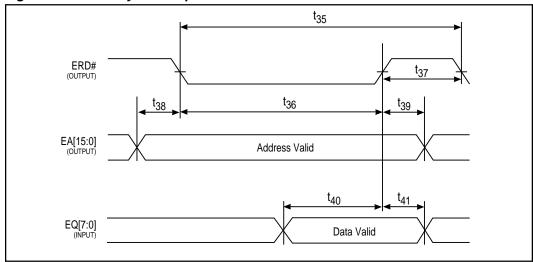

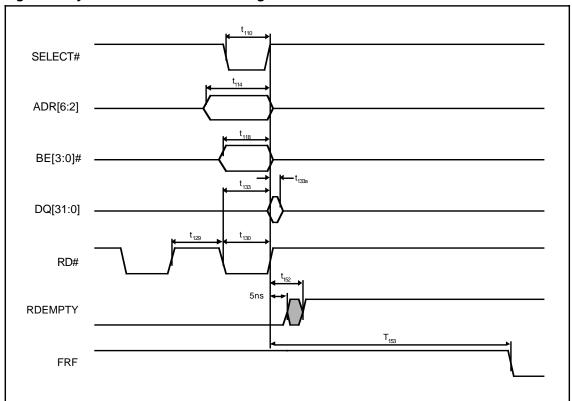

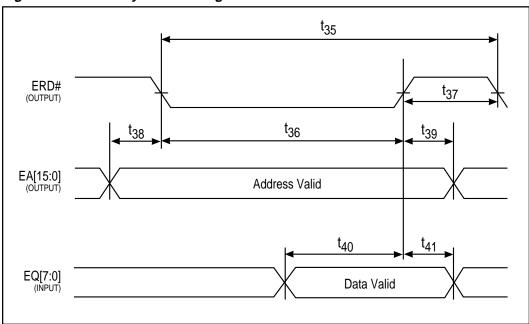

| Asynchronous RD# Register Access Timing         | 12-161 |

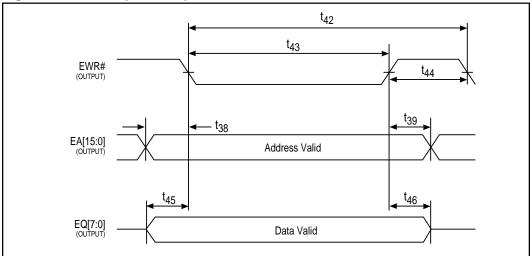

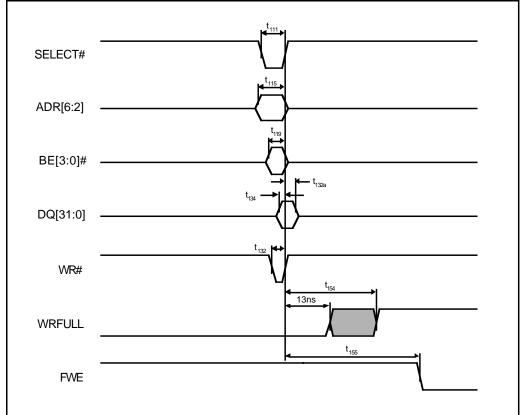

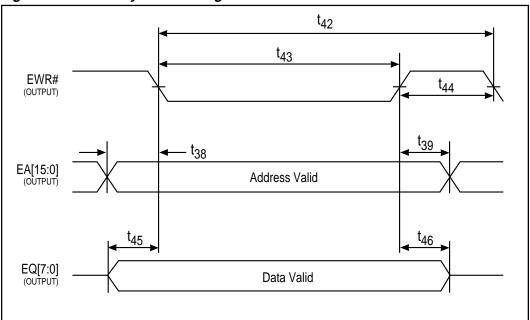

| Asynchronous WR# Register Access Timing         |        |

| Synchronous RD# FIFO Timing                     |        |

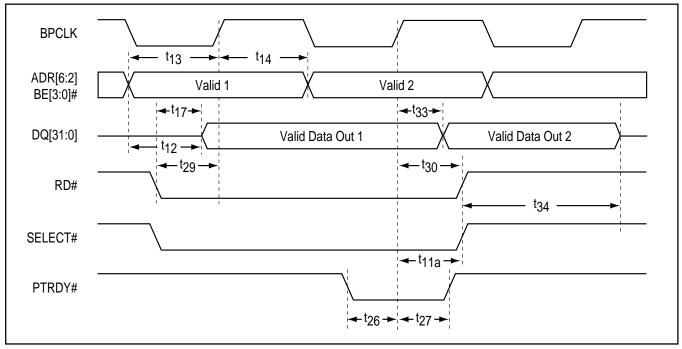

| Synchronous Multiple RD# FIFO Timing            |        |

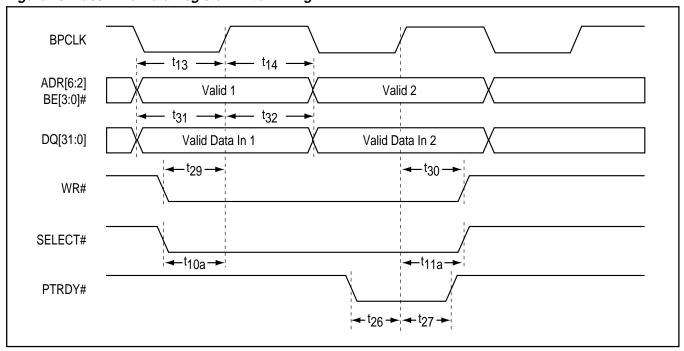

| Synchronous WR# FIFO Timing                     |        |

| Synchronous Multiple WR# FIFO Timing            | 12-166 |

| Target S5935 Pass-Thru Interface Timings        |        |

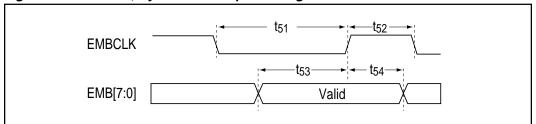

| Target Byte-Wide nv Memory Interface Timings    |        |

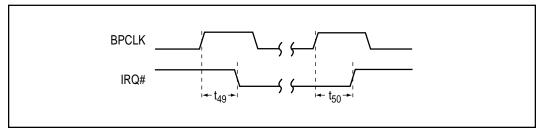

| Target Interrupt Timings                        | 12-171 |

| 13. PINOUT AND PACKAGE INFORMATION              |        |

| S5935 Pinout and Pin Assignment – 160 PQFP      |        |

| S5935 Pinout and Pin Assignment – 208 TQFP      |        |

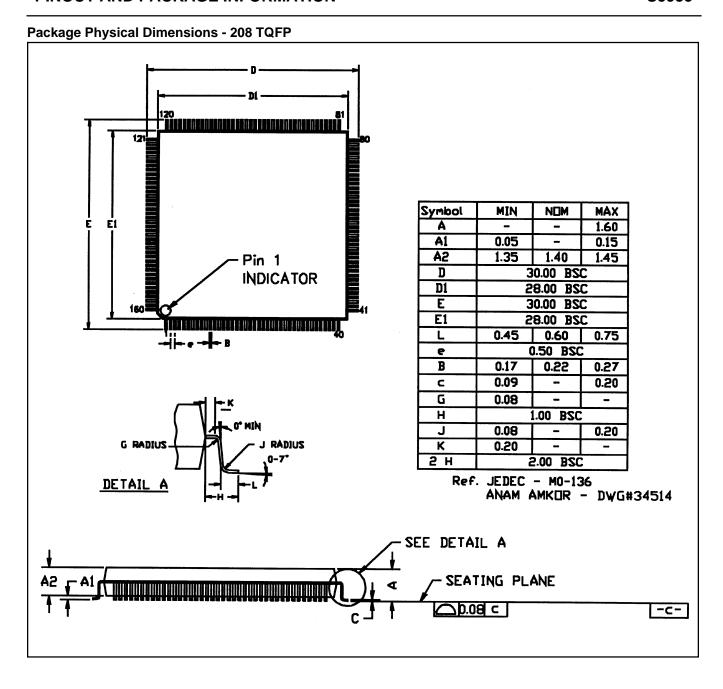

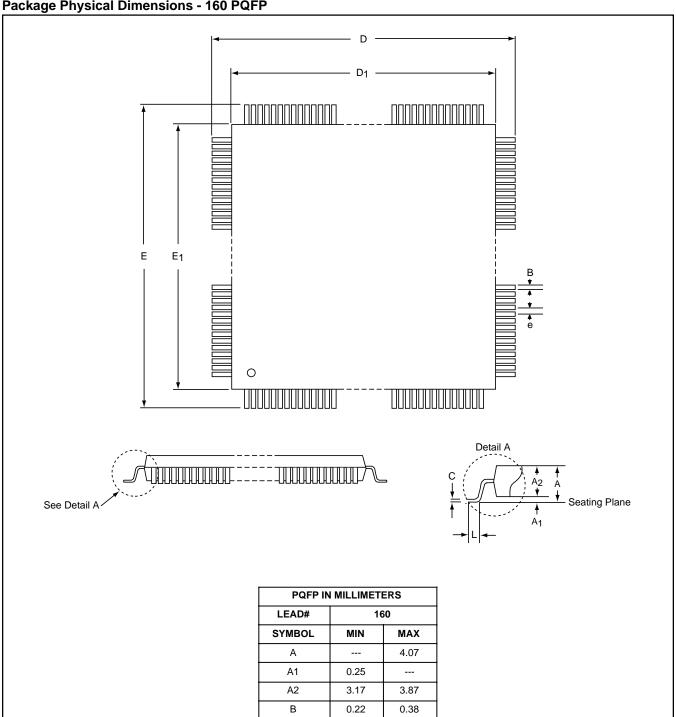

| Package Physical Dimensions – 160 PQFP          | 13-177 |

| Package Physical Dimensions – 208 TQFP          | 13-181 |

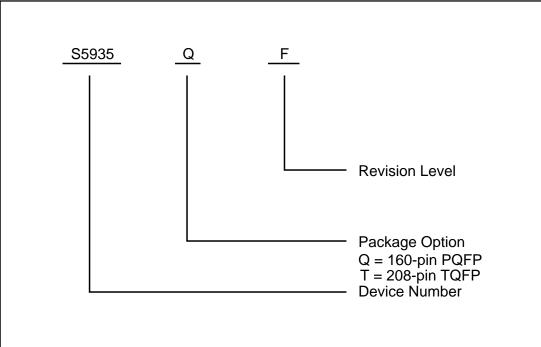

| Ordering Information                            |        |

[This page intentionally left blank.]

S5935

### **FEATURES**

- PCI 2.1 Compliant Master/Slave Device

- Full 132 Mbytes/sec Transfer Rate

- Supports new Intel 440BX/GX Chipsets

- Supports new WinNT Service Pack 2 & 3

- PCI Bus Operation DC to 33 MHz

- 8/16/32 Bit Add-On User Bus

- Four Definable Pass-Thru Data Channels

- Two 32 Byte Internal FIFOs w/DMA

- Synchronous Add-On Bus Operation

- Mail Box Registers w/Byte Level Status

- Direct Mail Box Data Strobe/Interrupts

- Direct PCI & Add-On Interrupt Pins

- Optional Non-Volatile Memory Boot Loading

- Optional Expansion BIOS/POST Code

#### **APPLICATIONS**

- High Speed Networking

- Digital Video Applications

- I/O Communications Ports

- High Speed Data Input/Output

- Multimedia Communications

- Memory Interfaces

- High Speed Data Acquisition

- Data Encryption/Decryption

- Intel i960 Interface

- General Purpose PCI Interfacing

- Existent S5933 Design Upgrades

### **DESCRIPTION**

The PCI Local bus concept was developed to break the PC data I/O bottleneck and clearly opens the door to increasing system speed and expansion capabilities. The PCI Local bus moves high speed peripherals from the I/O bus and places them closer to the system's processor bus, providing faster data transfers between the processor and peripherals. The PCI Local bus also addresses the industry's need for a bus standard which is not directly dependent on the speed, size and type of system processor. It represents the first microprocessor independent bus offering performance more than adequate for the most demanding applications such as full-motion video.

Applied Micro Circuits Corporation (AMCC), the premier supplier of single chip solutions, has developed the S5935 to solve the problem of interfacing applications to the PCI Local bus while offering support for newer PCI chipsets and operating systems. The S5935 is a powerful and flexible PCI controller supporting several levels of interface sophistication. At the lowest level, it can serve simply as a PCI bus Target with modest transfer requirements. For high-performance applications, the S5935 can become a Bus Master to attain the PCI Local bus peak transfer capability of 132 MBytes/sec. The S5935 PCI controller also maintains drop-in compatibility for upgrading many existent S5933 designs requiring migration into new motherboard architectures, PCI BIOSs and software operating systems.

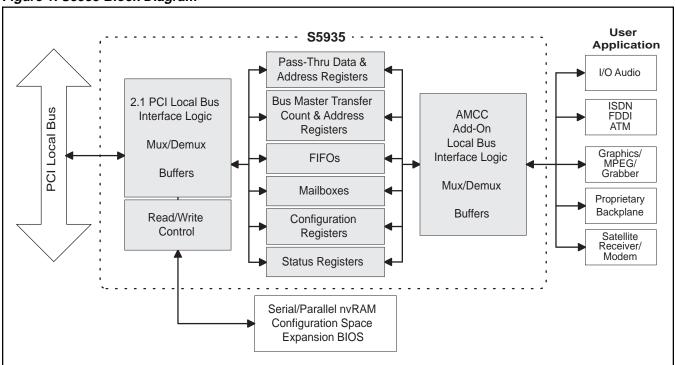

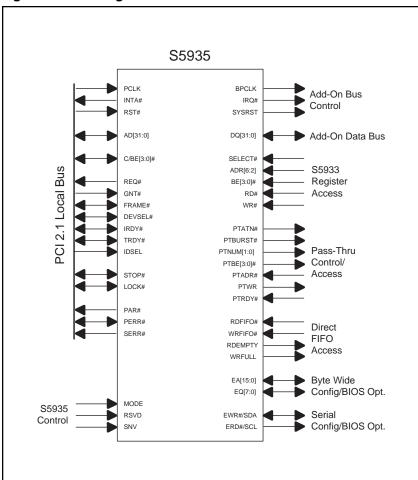

Figure 1. S5935 Block Diagram

The S5935 is an off-the-shelf, low-cost, standard product, which is PCI 2.1 compliant. And, since AMCC is a member of the PCI Special Interest Group, the S5935 has been tested on various manufacturer's PCI motherboards, chip sets, PCI BIOSs and operating systems. This removes the burden of compliance and compatibility testing from the designer and thus significantly reduces development time. Utilizing the S5935 allows the designer to focus on the actual application, not debugging the PCI interface.

The S5935 allows special direct data accessing between the PCI bus and the user application through implementation of four definable Pass-Thru data channels. Each data channel is implemented by defining a Host memory segment size and 8/16/32-bit user bus width. The addition of two 32 byte FIFOs, also used in S5935 Bus Mastering applications, provides further versatility to data transfer capabilities. FIFO DMA transfers are supported using Address and Transfer Count Registers. Four 32-bit Mailbox Registers coupled with a Status Register and extensive interrupt capabilities provide flexible user command or message transfers between the two buses. In addition, the S5935 also allows use of an external serial, or byte-wide nonvolatile memory to perform any pre-boot initialization requirements and to provide custom expansion BIOS or POST code capability.

#### **S5935 ARCHITECTURE**

The block diagram in Figure 1 above shows the major functional elements within the S5935. The S5935 provides three physical bus interfaces: the PCI Local bus, the user local bus referred to as the Add-On Local bus and the optional serial and byte-wide non-volatile memory buses. Data movement between buses can take place through mailbox registers or the FIFO data channel, or a user can define and enable one or more of the four Pass-Thru data channels. S5935 Bus Master or DMA data transfers to and from the PCI Local bus are performed through the FIFO data channel under either Host or Add-On software control or Add-On hardware control using dedicated S5935 signal pins.

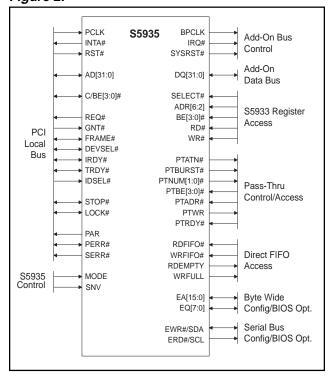

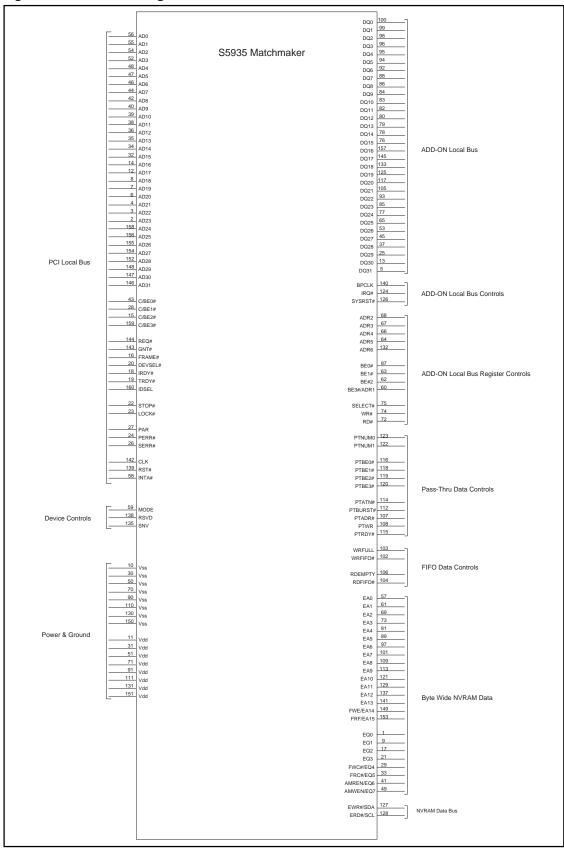

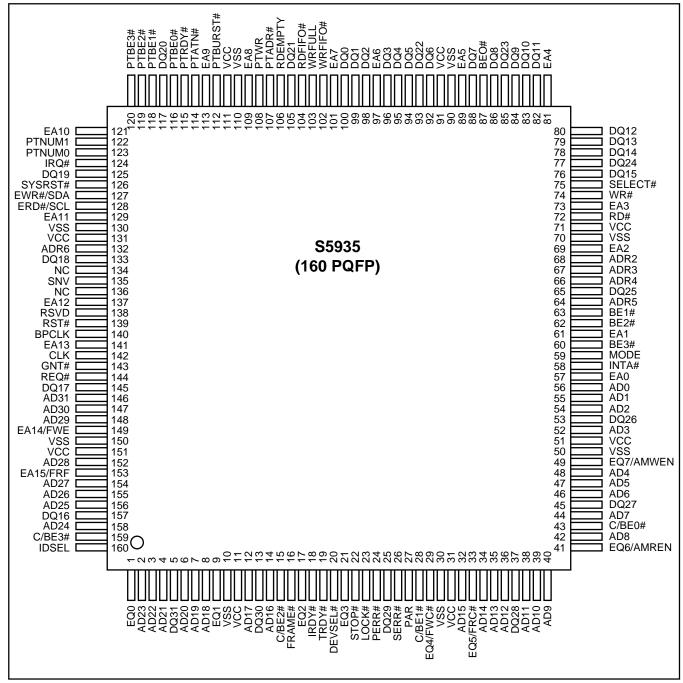

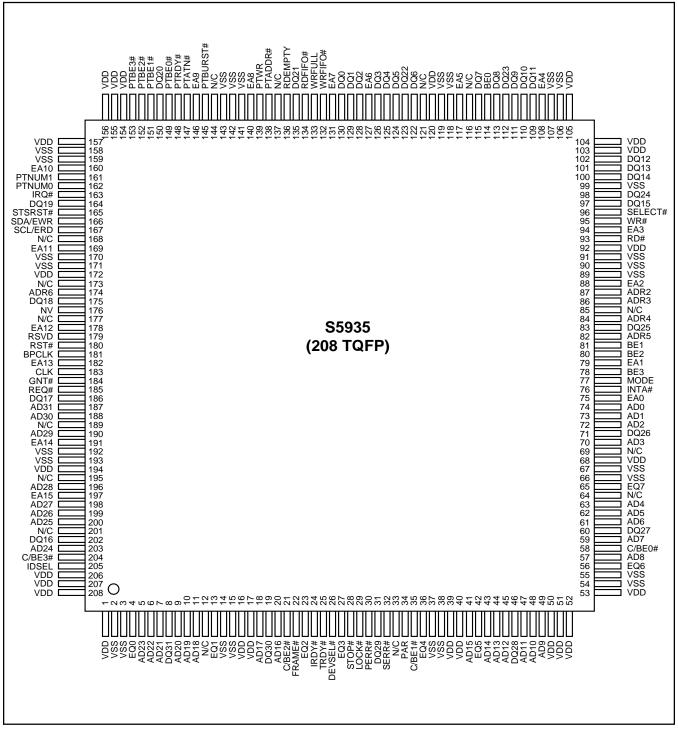

The S5935 signal pins are shown in Figure 2. The PCI Local Bus signals are detailed on the left side; Add-On Local Bus signal are detailed on the right side. All additional S5935 device control signals are shown on the lower right side.

The S5935 supports a two wire serial nvRAM bus and a byte-wide EPROM/FLASH bus. This allows the designer to customize the S5935 configuration by loading setup information on system power-up.

Figure 2.

#### S5935 Register Architecture

Control and configuration of the Add-On Local bus, and the S5935 itself, is performed through three primary groups of registers. These groups consist of PCI Configuration Registers, PCI Operation Registers and Add-On Operation Registers. These registers are user configurable through either their associated bus or from an external non-volatile memory device. This section will provide a brief overview of each of these register groups and the optional non-volatile interface.

#### **PCI Configuration Registers**

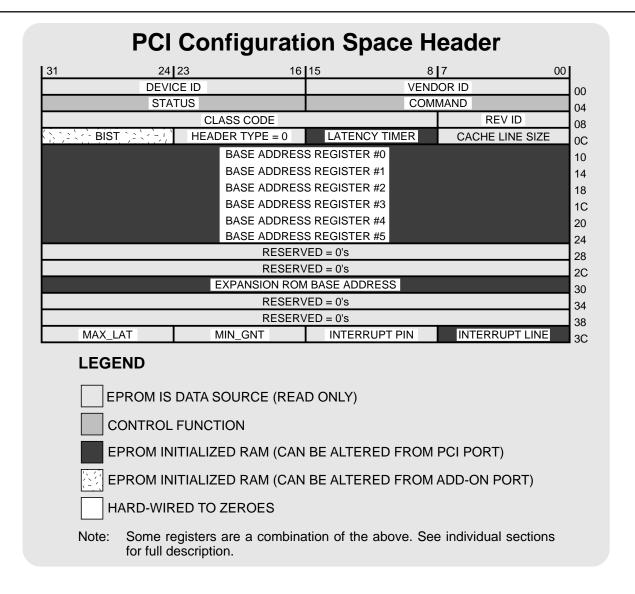

All PCI compliant devices are required to provide a group of Configuration Registers for the host system. These registers are polled during power up initialization and contain specific device and add-in card product information including Vendor ID, Device ID, Revision and the amount of memory required for product operation. The S5935 can either load these registers with default values or initialize them from an external nonvolatile memory area called 'Configuration Space'. The S5935 can accommodate a total of 256 bytes of external memory for this purpose. The first 64 bytes is reserved for user defined configuration data which is loaded into the PCI Configuration Registers during power-up initialization. The remaining 192 bytes may be used to implement an Expansion BIOS or contain add-in card POST code. Table 1 shows all the S5935 PCI Configuration Registers.

S5935

Table 1. PCI Configuration Registers

| Byte 3                                                | Byte 2      | Byte 1        | Byte 0          | Address |

|-------------------------------------------------------|-------------|---------------|-----------------|---------|

| Device ID                                             |             | Vendor ID     |                 | 00h     |

| PCI S                                                 | Status      | PCI Co        | mmand           | 04h     |

|                                                       | Class Code  | -             | Revision ID     | 08h     |

| Built-in Self Test                                    | Header Type | Latency Timer | Cache Line Size | 0Ch     |

|                                                       | Base Addres | ss Register 0 |                 | 10h     |

|                                                       | Base Addres | ss Register 1 |                 | 14h     |

|                                                       | Base Addres | ss Register 2 |                 | 18h     |

| Base Address Register 3 10                            |             |               | 1Ch             |         |

| Base Address Register 4                               |             |               | 20h             |         |

| Reserved                                              |             |               | 24h             |         |

| Reserved Space                                        |             |               | 28h             |         |

| Reserved Space 2Ch                                    |             |               | 2Ch             |         |

| Expansion ROM Base Address 30h                        |             |               | 30h             |         |

| Reserved Space 34h                                    |             |               | 34h             |         |

| Reserved Space                                        |             |               | 38h             |         |

| Max. Latency Min. Grant Interrrupt Pin Interrupt Line |             |               |                 | 3Ch     |

## **PCI Operation Registers**

The second group of registers are the PCI Operation Registers shown in Table 2. This group consists of sixteen 32-bit (DWORD) registers accessible to the Host processor from the PCI Local bus. These are the main registers through which the PCI Host configures S5935 operation and communicates with the Add-On Local bus. These registers encompass the PCI bus incoming and outgoing Mailboxes, FIFO data channel, Bus Master Address and Count registers, Pass-Thru data channel registers and S5935 device Status and Control registers.

#### **Add-On Bus Operation Registers**

The third and last register group consists of the Add-On Operation Registers, shown in Table 3. This group of eighteen 32-bit (DWORD) registers is accessible to the Add-On Local bus. These are the main registers through which the Add-On logic configures S5935 operation and communicates with the PCI Local bus. These registers encompass the Add-On bus Mailboxes, Add-On FIFO, DMA Address/Count Registers (when Add-On initiated Bus Mastering), Pass-Thru Registers and Status/Control registers.

Table 2. PCI Operation Registers

| PCI Operation Registers                     | Address<br>Offset |

|---------------------------------------------|-------------------|

| Outgoing Mailbox Register 1 (OMB1)          | 00h               |

| Outgoing Mailbox Register 2 (OMB2)          | 04h               |

| Outgoing Mailbox Register 3 (OMB3)          | 08h               |

| Outgoing Mailbox Register 4 (OMB4)          | 0Ch               |

| Incoming Mailbox Register 1 (IMB1)          | 10h               |

| Incoming Mailbox Register 2 (IMB2)          | 14h               |

| Incoming Mailbox Register 3 (IMB3)          | 18h               |

| Incoming Mailbox Register 4 (IMB4)          | 1Ch               |

| FIFO Register Port (bidirectional) (FIFO)   | 20h               |

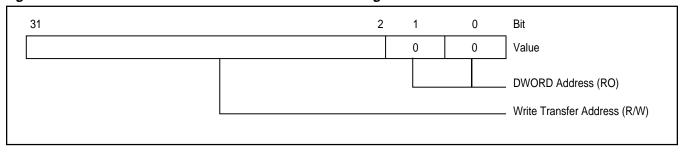

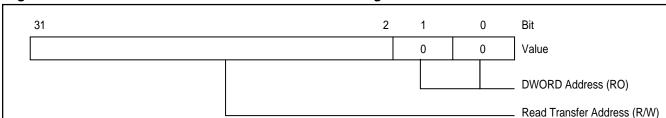

| Master Write Address Register (MWAR)        | 24h               |

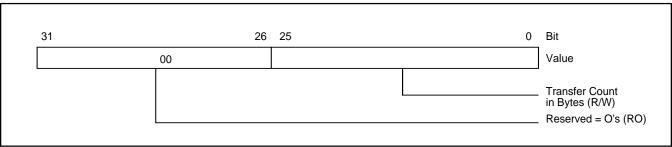

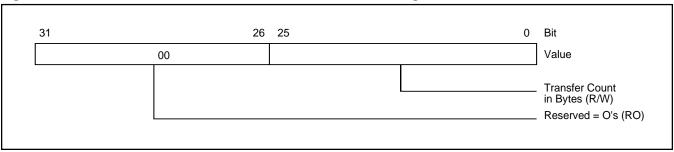

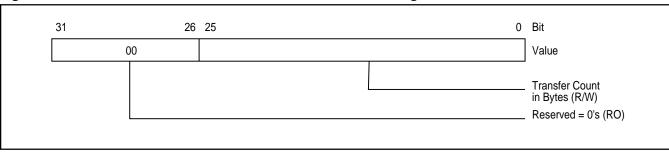

| Master Write Transfer Count Register (MWTC) | 28h               |

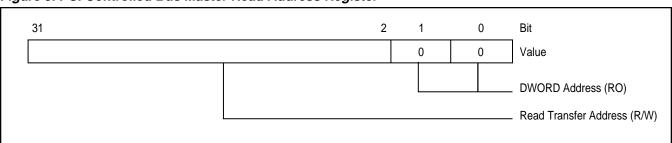

| Master Read Address Register (MRAR)         | 2Ch               |

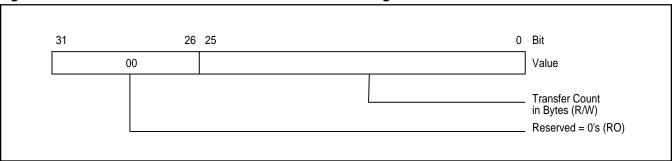

| Master Read Transfer Count Register (MRTC)  | 30h               |

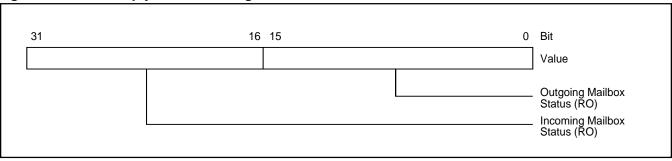

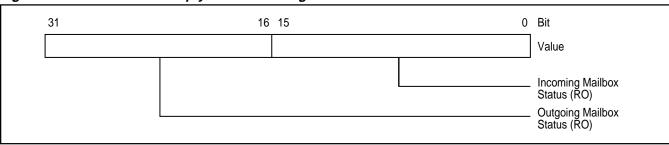

| Mailbox Empty/Full Status Register (MBEF)   | 34h               |

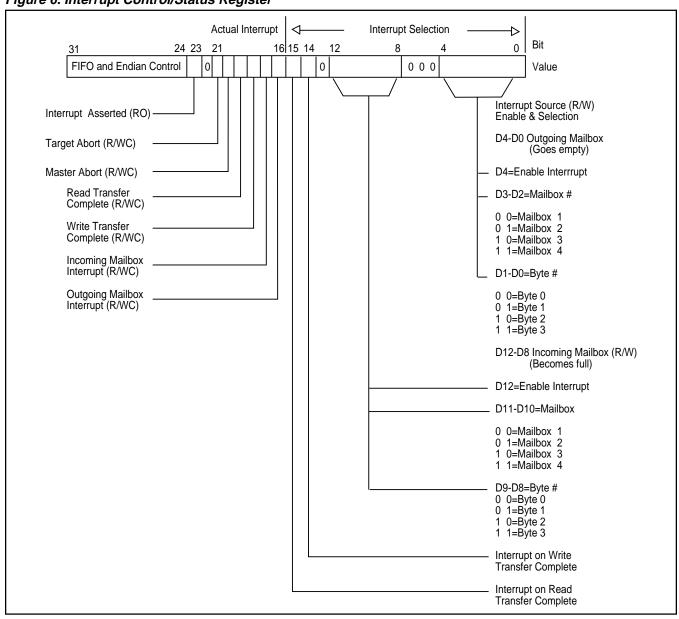

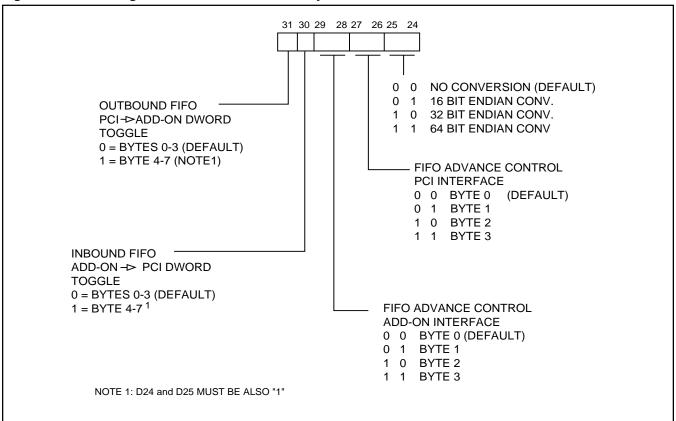

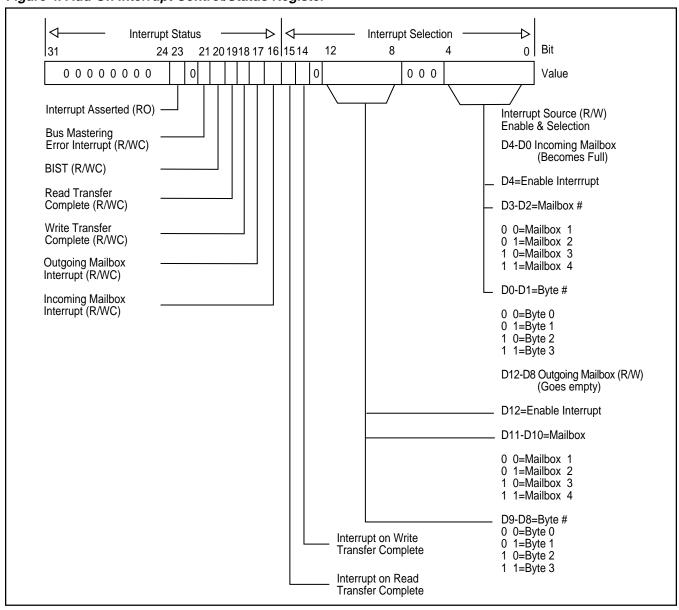

| Interrupt Control/Status Register (INTCSR)  | 38h               |

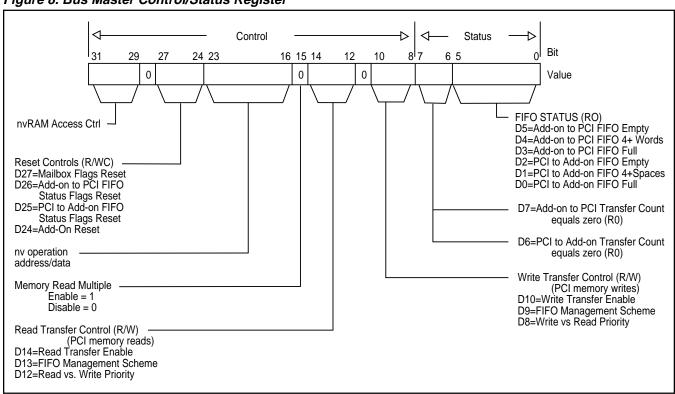

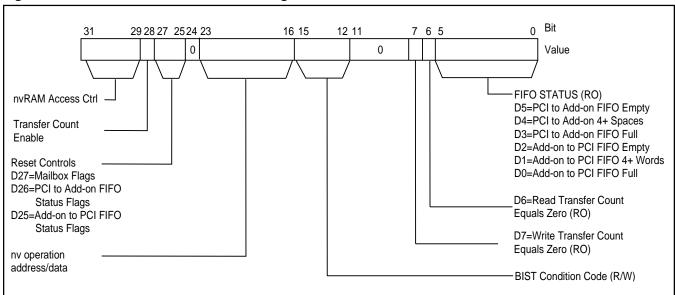

| Bus Master Control/Status Register (MCSR)   | 3Ch               |

### **Non-Volatile Memory Interface**

The S5935 contains a set of PCI Configuration Registers. These registers can be initialized with default values or with designer specified values contained in an external nvRAM. The nvRAM can be either a serial (2 Kbytes, maximum) or a byte-wide device (64 Kbytes, maximum).

The optional nvRAM allows the Add-On card manufacturer to initialize the S5935 with his specific Vendor ID and Device ID numbers along with desired S5935 operation characteristics. The non-volatile memory feature also provides for the Expansion BIOS and POST code (power-on-self-test) options on the PCI bus.

Table 3. Add-On Bus Operation Registers

| Add-On Bus Operation Registers             | Address |

|--------------------------------------------|---------|

| Incoming Mailbox Register 1 (AIMB1)        | 00h     |

| Incoming Mailbox Register 2 (AIMB2)        | 04h     |

| Incoming Mailbox Register 3 (AIMB3)        | 08h     |

| Incoming Mailbox Register 4 (AIMB4)        | 0Ch     |

| Outgoing Mailbox Register 1 (AOMB1)        | 10h     |

| Outgoing Mailbox Register 2 (AOMB2)        | 14h     |

| Outgoing Mailbox Register 3 (AOMB3)        | 18h     |

| Outgoing Mailbox Register 4 (AOMB4)        | 1Ch     |

| FIFO Port (AFIFO)                          | 20h     |

| Bus Master Write Address Register (MWAR)   | 24h     |

| Pass-Thru Address Register (APTA)          | 28h     |

| Pass-Thru Data Register (APTD)             | 2Ch     |

| Bus Master Read Address Register (MRAR)    | 30h     |

| Mailbox Empty/Full Status Register (AMBEF) | 34h     |

| Interrupt Control/Status Register (AINT)   | 38h     |

| General Control/Status Register (ARCR)     | 3Ch     |

| Bus Master Write Transfer Count (MWTC)     | 58h     |

| Bus Master Read Transfer Count (MRTC)      | 5Ch     |

### **Mailbox Operation**

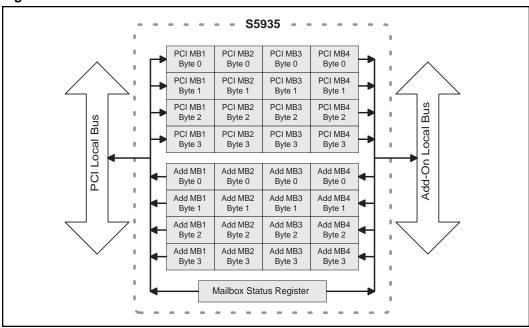

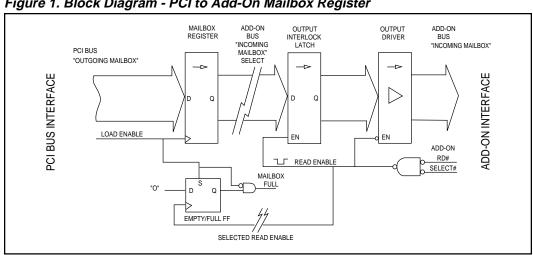

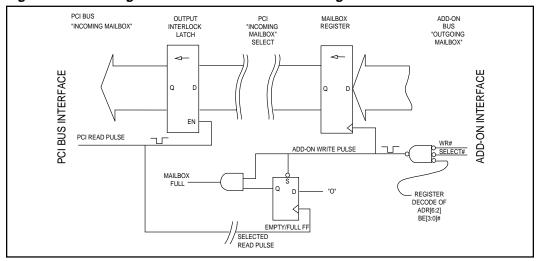

The Mailbox Registers are divided into two four DWORD sets. Each set is dedicated to one bus for transferring data to the other bus. Figure 3 below shows a block diagram of the mailbox section of the S5935. The provision of Mailbox Registers provides an easy path for the transfer of user information (command, status or parametric data) between the two buses. An empty/full indication for each Mailbox Register, at the byte level, is determined by polling a Status Register accessible to both the PCI and Add-On buses. Providing Mailbox byte level empty/full indications allows for greater flexibility in 8-, 16- or 32-bit system interfaces. i.e., transferring a single byte to an 8-bit Add-On bus without requiring the assembling or disassembling of 32-bit data.

The generation of interrupts from Mailbox Registers is equivalent with the commonly known 'DOORBELL' interrupt technique. Bit locations configured within the S5935's Operation Registers select a Mailbox and Mailbox byte which is to generate an interrupt when full or touched. A mailbox interrupt control register is then used to enable interrupt generation and to select if the interrupt is to be generated on the PCI or Add-On Local bus. PCI Local bus interrupts may also be generated from direct hardware interfacing due to a unique AMCC feature. A dedicated Mailbox byte is directly accessible via a set of hardware device signal pins. A mailbox load signal pin latches Add-On bus data directly into the Mailbox initiating a PCI bus interrupt if enabled. Mailbox data may also be read in a similar manner. This option is shared with the byte wide non-volatile memory signal pins. The S5935 must use the serial nvRAM for the direct mailbox option signal pins to be available or they are assigned to the byte wide at power up.

Figure 3.

### **Pass-Thru Operation**

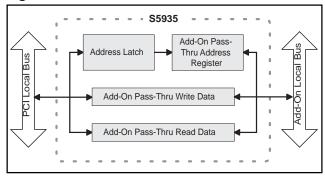

Pass-Thru operation executes PCI bus cycles in real time with the Add-On bus. This allows the PCI bus to directly read or write to Add-On resources. The S5935 allows the designer to declare up to four individual Pass-Thru Regions. Each region may be defined as 8, 16-, or 32-bits wide, mapped into host memory or I/O space and may be up to 512MB bytes in size. Figure 4 right shows a block diagram of the S5935 Pass-Thru architecture.

Pass-Thru operations are performed in PCI target only mode, making this data channel useful for converting existing ISA or EISA designs over to the fast PCI architecture. The Pass-Thru data channel utilizes separate Add-On bus signal pins to reflect a PCI bus read or write request. Add-On logic decodes these signals to determine if it must read or write data to the S5935 to satisfy the request. Information decoded includes PCI request occurring, the byte lanes involved, the specific Pass-Thru region accessed and if the request is a burst or single-cycle access. All requested Pass-Thru address and data information is passed via Add-On Operation Registers.

Pass-Thru operation supports single PCI data cycles and PCI data bursts. During PCI burst operations, the S5935 is capable of transferring data at the full PCI bandwidth. Should slower Add-On logic be implemented, the S5935 automatically issues PCI bus waits or a Host retry indication until the requested transfer is satisfied.

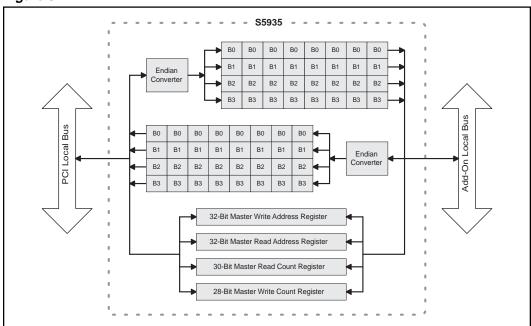

### **FIFO PCI Bus Mastering Operation**

FIFO PCI Bus Master data transfers are processed by one of two 8-DWORD FIFOs. The FIFO block diagram is shown in Figure 5. The particular FIFO selected for a data transfer is dependent only on the direction of data flow and is completely transparent to the user. Internal S5935 decode logic selects the FIFO that is dedicated to transferring data to the other bus.

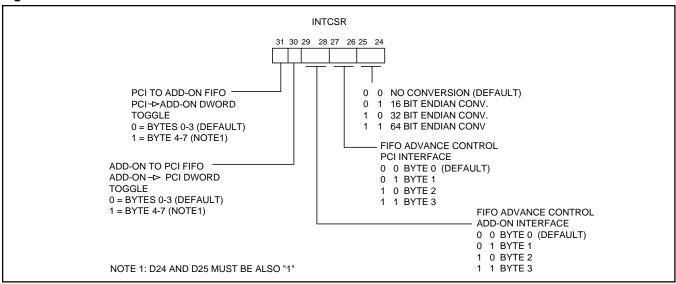

The way data is transferred by a FIFO, is determined by Operation and Configuration Registers contained within the S5935. A FIFO may be configured for either PCI or Add-On initiated Bus Mastering with programmable byte advance conditions, read vs. write priorities and Add-On bus widths. Advance conditions allow the FIFO to implement 8-, 16- or 32-bit bus widths. Configuring the S5935 for Bus Master operation enables separate

Figure 4.

address and data count registers, which are loaded with the PCI memory address location and number of bytes to be read or written. This is accomplished by either the Host CPU or Add-On logic. Data can be transferred between the two buses transparent to the PCI Host processor, however, the Add-On logic is required to service the S5935 Add-On Local bus. An indication of transfer completion can be seen by polling a status register done bit or S5935 signal pin or enabling a 'transfer count = 0' interrupt to either bus.

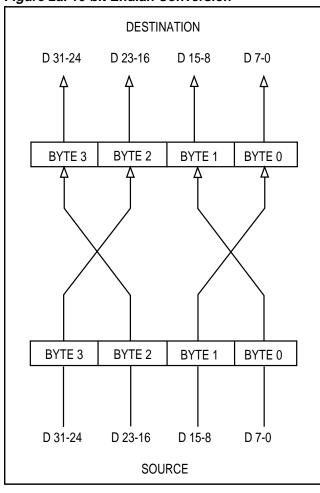

Further FIFO configuration bits select 16, 32, or 64 bit Endian conversion options for incoming and outgoing data. Endian conversion allows an Add-On processor and the host to transfer data in their native Endian format. Other configuration bits determine if the Add-On Local bus width is 8, 16 or 32 bits. 16-bit bus configurations internally steer FIFO data from the upper 16 bits of the DWORD and then to the lower 16-bits on alternate accesses. FIFO pointers are then updated when appropriate bytes are accessed. Other methods are available for 8-bit or 16-bit Add-Ons.

Efficient FIFO management configuration schemes unique to the AMCC S5935 specify how full or empty a FIFO must be before it requests the PCI Local bus. These criteria include bus requests when any of the 8 DWORDs are empty, or when four or more DWORDs are empty. This allows the designer to control how often the S5935 requests the bus. The S5935 always attempts to perform burst operations to empty or fill the FIFOs. Further FIFO capabilities over the standard register access methods allow for direct hardware FIFO access. This is provided through separate access pins on the S5935. Other status output pins allow for easily cascading external FIFOs to the Add-On design.

Figure 5.

Figure 8. S5933 Pin Assignment

[This page intentionally left blank.]

### **Signal Type Definition**

SIGNAL DESCRIPTIONS

The following signal type definitions [in, out, t/s, s/t/s and o/d] are taken from Revision 2.1 of the PCI local bus specification.

in Input is a standard input-only signal.

**out** Totem Pole Output is a standard active driver.

t/s Tri-State® is a bidirectional, tristate input/output pin.

**s/t/s** Sustained Tri-State is an active low tristate signal owned and driven by one and only one agent at a time. The agent that drives an s/t/s pin low must drive it high for at least one clock before letting it float. A new agent cannot start driving a s/t/s signal any sooner than one clock after the previous owner tri-states it. A pullup is required to sustain the inactive state until another agent drives it, and must be provided by the central source.

**o/d** Open Drain allows multiple devices to share as a wire-OR.

Note that a # symbol at the end of a signal name denotes that the active state occurs when the signal is at a low voltage. When no # symbol is present, the signal is active high.

Figure 1. S5935 Signal Pins

# **PCI BUS INTERFACE SIGNALS**

# Address and Data Pins — PCI Local Bus

| Signal     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AD[31:00]  | t/s  | Local Bus Address/Data lines. Address and data are multiplexed on the same pins. Each bus operation consists of an address phase followed by one or more data phases. Address phases are identified when the control signal, FRAME#, is asserted. Data transfers occur during those clock cycles in which control signals IRDY# and TRDY# are both asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| C/BE[3:0]# | t/s  | Bus Command and Byte Enables. These are multiplexed on the same pins. During the address phase of a bus operation, these pins identify the bus command, as shown in the table below. During the data phase of a bus operation, these pins are used as Byte Enables, with C/BE[0]# enabling byte 0 (least significant byte) and C/BE[3]# enabling byte 3 (most significant byte).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|            |      | C/BE[3:0]# Description (during address phase)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|            |      | 0         0         0         Interrupt Acknowledge           0         0         0         1         Special Cycle           0         0         1         0         I/O READ           0         0         1         1         I/O WRITE           0         1         0         0         Reserved           0         1         0         1         Reserved           0         1         1         0         Memory Write           1         0         0         0         Reserved           1         0         0         1         Reserved           1         0         1         0         Configuration Read           1         0         1         1         Configuration Write           1         1         0         0         MEMORY READ - Multiple           1         1         0         1         Dual Address Cycle           1         1         1         0         Memory Read Line |  |  |

| PAR        | t/s  | Parity. This signal is even parity across the entire AD[31:00] field along with the C/BE[3:0]# field. The parity is stable in the clock following the address phase and is sourced by the master. During the data phase for write operations, the bus master sources this signal on the clock following IRDY# active; during the data phase for read operations, this signal is sourced by the target and is valid on the clock following TRDY# active. The PAR signal therefore has the same timing as AD[31:00}, delayed by one clock.                                                                                                                                                                                                                                                                                                                                                                          |  |  |

# **SIGNAL DESCRIPTIONS**

# System Pins — PCI Local Bus

| Signal | Туре | Description                                                                                                                                                                                                                         |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK    | in   | Clock. The rising edge of this signal is the reference upon which all other signals are based, with the exception of RST# and the interrupt (IRQA#-). The maximum frequency for this signal is 33 MHz and the minimum is DC (0 Hz). |

| RST#   | in   | Reset. This signal is used to bring all other signals within this device to a known, consistent state. All PCI bus interface output signals are not driven (tri-stated), and open drain signals such as SERR# are floated.          |

# Interface Control Pins — PCI Bus Signal

| Signal  | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FRAME#  | s/t/s | Frame. This signal is driven by the current bus master and identifies both the beginning and duration of a bus operation. When FRAME# is first asserted, it indicates that a bus transaction is beginning and that valid addresses and a corresponding bus command are present on the AD[31:00] and C/BE[3:0] lines. FRAME# remains asserted during the data transfer portion of a bus operation and is deasserted to signify the final data phase. |

| IRDY#   | s/t/s | Initiator Ready. This signal is sourced by the bus master and indicates that the bus master is able to complete the current data phase of a bus transaction. For write operations, it indicates that valid data is on the AD[31:00] pins. Wait states occur until both TRDY# and IRDY# are asserted together.                                                                                                                                       |

| TRDY#   | s/t/s | Target Ready. This signal is sourced by the selected target and indicates that the target is able to complete the current data phase of a bus transaction. For read operations, it indicates that the target is providing valid data on the AD[31:00] pins. Wait states occur until both TRDY# and IRDY# are asserted together.                                                                                                                     |

| STOP#   | s/t/s | Stop. The Stop signal is sourced by the selected target and conveys a request to the bus master to stop the current transaction.                                                                                                                                                                                                                                                                                                                    |

| LOCK#   | in    | Lock. The lock signal provides for the exclusive use of a resource. The S5935 may be locked as a target by one master at a time. The S5935 cannot lock a target when it is a master.                                                                                                                                                                                                                                                                |

| IDSEL   | in    | Initialization Device Select. This pin is used as a chip select during configuration read or write operations.                                                                                                                                                                                                                                                                                                                                      |

| DEVSEL# | s/t/s | Device Select. This signal is sourced by an active target upon decoding that its address and bus commands are valid. For bus masters, it indicates whether any device has decoded the current bus cycle.                                                                                                                                                                                                                                            |

# SIGNAL DESCRIPTIONS

# Arbitration Pins (Bus Masters Only) — PCI Local Bus

| Signal | Туре | Description                                                                                                                                               |

|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| REQ#   | out  | Request. This signal is sourced by an agent wishing to become the bus master. It is a point-to-point signal and each master has its own REQ#.             |

| GNT#   | in   | Grant. The GNT# signal is a dedicated, point-to-point signal provided to each potential bus master and signifies that access to the bus has been granted. |

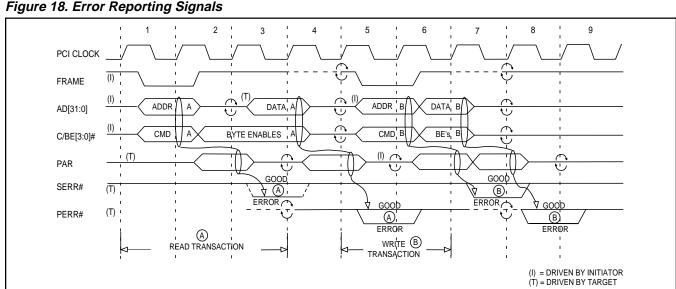

# Error Reporting Pins — PCI Local Bus

| Signal | Туре  | Description                                                                                                                                                                                                                                                                                                                                                          |

|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PERR#  | s/t/s | Parity Error. This pin is used for reporting parity errors during the data portion of a bus transaction for all cycles except a Special Cycle. It is sourced by the agent receiving data and driven active two clocks following the detection of the error. This signal is driven inactive (high) for one clock cycle prior to returning to the tri-state condition. |

| SERR#  | o/d   | System Error. This pin is used for reporting address parity errors, data parity errors on Special Cycle commands, or any error condition having a catastrophic system impact.                                                                                                                                                                                        |

# Interrupt Pin — PCI Local Bus

| Signal | Туре | Description                                                                                                                                                                      |

|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTA#  | o/d  | Interrupt A. This pin is a level sensitive, low active interrupt to the host. The INTA# interrupt must be used for any single function device requiring an interrupt capability. |

### **NON-VOLATILE MEMORY INTERFACE SIGNALS**

This signal grouping provides for connection to external non-volatile memories. Either a serial or byte-wide device may be used.

The serial interface shares the read and write control pins used for interfacing with byte-wide memory devices. Since it is intended that only one (serial or byte wide) configuration be used in any given implementation, separate descriptions are provided for each. The S5935 provides the pins necessary to interface to a byte wide non-volatile memory. When they are connected to a properly configured serial memory, these byte wide interface pins assume alternate functions. These alternate functions include added external FIFO status flags, FIFO reset control, Add-On control for bus mastering and a hardware interface mailbox port.

### Serial nv Devices

| Signal | Туре | Description                                                                                                                                                                                                                                                                                                                    |

|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

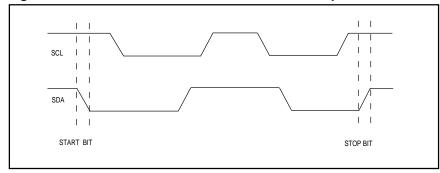

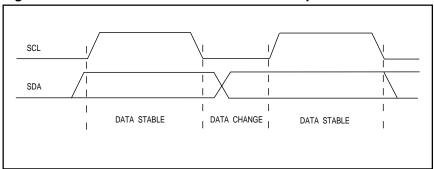

| SCL    | t/s  | Serial Clock. This output is intended to drive a two-wire Serial Interface and functions as the bus's master. It is intended that this signal be directly connected to one or more inexpensive serial non-volatile RAMs or EEPROMs. This pin is shared with the byte wide interface signal, ERD#.                              |

| SDA    | t/s  | Serial Data/Address. This bidirectional pin is used to transfer addresses and data to or from a serial nvRAM or EEPROM. It is an open drain output and intended to be wire-ORed with all other devices on the serial bus using a 4.7K external pull-up resistor. This pin is shared with the byte wide interface signal, EWR#. |

| SNV    | in   | Serial Non-Volatile Device. This input, when high, indicates a serial boot device or no boot device is present. When this pin is low, a byte-wide boot device is present.  Note: SCL and SDA are not controlled by FLT#.                                                                                                       |

#### Byte-Wide nv Devices

| Signal    | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EA[15:00] | t/s  | External nv memory address. These signals connect directly to the external BIOS (or EEPROM) or EPROM address pins EA0 through EA15. The PCI interface controller assembles 32-bit-wide accesses through multiple read cycles of the 8-bit device. The address space from 0040h through 007Fh is used to preload and initialize the PCI configuration registers. Should an external nv memory be used, the minimum size required is 128 bytes and the maximum is 64K bytes. When a serial memory is connected to the S5935, the pins EA[7:0] are reconfigured to become a hardware Add-On to PCI mailbox register with the EA8 pin as the mailbox load clock. Also, the EA15 signal pin will provide an indication that the PCI to Add-On FIFO is full (FRF#), and the EA14 signal pin will indicate whether the Add-On to PCI FIFO is empty (FWE#). |

| ERD#      | out  | External nv memory read control. This pin is asserted during read operations involving the external non-volatile memory. Data is transferred into the S5935 during the low to high transition of ERD#. This pin is shared with the serial external memory interface signal, SCL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| EWR#      | t/s  | External nv memory write control. This pin is asserted during write operations involving the external non-volatile memory. Data is presented on pins EQ[7:0] along with its address on pins EA[15:0] throughout the entire assertion of EWR#. This pin is shared with the serial external memory interface signal, SDA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| EQ[7:0]   | t/s  | External memory data bus. These pins are used to directly connect with the data pins of an external non-volatile memory. When a serial memory is connected to the S5935, the pins EQ4, EQ5, EQ6 and EQ7 become reconfigured to provide signal pins for bus mastering control from the Add-On interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# **ADD-ON BUS INTERFACE SIGNALS**

The following sets of signals represent the interface pins available for the Add-On function. There are four groups: Register access, FIFO access, Pass-Thru mode pins, and general system pins.

### Register Access Pins

| Signal          | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

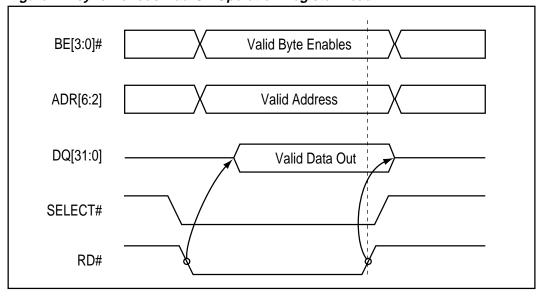

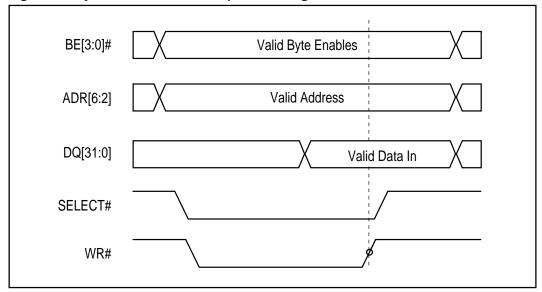

| DQ[31:00]       | t/s  | Datapath DQ0–DQ31. These pins represent the datapath for the Add-On peripheral's data bus. They provide the interface to the controller's FIFO and other registers. When MODE=V <sub>CC</sub> , only DQ[15:00] are used. DQ[31:0] have internal pull-up resistors.                                                                                                                                              |  |

| ADR[6:2]        | in   | Add-On Addresses. These signals are the address lines to select which of the 16 DWORD registers within the controller is desired for a given read or write cycle, as shown in the table below.                                                                                                                                                                                                                  |  |

|                 |      | Register Name                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| BE3# or<br>ADR1 | in   | Byte Enable 3 (32-bit mode) or ADR1 (16 bit mode). This pin is used in conjunction with the read or write strobes (RD# or WR#) and the Add-On select signal, SELECT#. As a Byte Enable, it is necessary to have this pin asserted to perform write operations to the register identified by ADR[6:2] bit locations d24 through d31; for read operations it controls the DQ[31:24] output drive.                 |  |

| BE[2:0]#        | in   | Byte Enable 2 through 0. These pins provide for individual byte control during register read or write operations. BE2# controls activity over DQ[23:DQ16], BE1# controls DQ[15:8], and BE0# controls DQ[7:0]. During read operations they control the output drive for each of their respective byte lanes; for write operations they serve as a required enable to perform the modification of each byte lane. |  |

| SELECT#         | in   | Select for the Add-On interface. This signal must be driven low for any write or read access to the Add-On interface registers. This signal must be stable during the assertion of command signals WR# or RD#.                                                                                                                                                                                                  |  |

| WR#             | in   | Write strobe. This pin, when asserted in conjunction with the SELECT# pin, causes the writing of one of the internal registers. The specific register and operand size are identified through address pins ADR[6:2] and the byte enables, BE[3:0]#.                                                                                                                                                             |  |

| RD#             | in   | Read strobe. This pin, when asserted in conjunction with the SELECT# pin, causes the reading of one of the internal registers. The specific register and operand size are identified through address pins ADR[6:2] and the byte enables BE[3:0]#.                                                                                                                                                               |  |

| MODE            | in   | This pin control whether the S5935 data accesses on the DQ bus are to be 32-bits wide (MODE = low) or 16-bits wide (MODE = high). When in the 16 bit mode, the signal BE3# is reassigned as the address signal ADR1.                                                                                                                                                                                            |  |

# **SIGNAL DESCRIPTIONS**

# FIFO Access Pins

| Signal  | Туре | Description                                                                                                                                                                                                                                                                                                                                                  |

|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WRFIFO# | in   | Write FIFO. This signal provides a method to directly write the FIFO without having to generate the SELECT# signal or the ADR[6:2] value of [01000b] to access the FIFO. Access width is either 32 bits or 16 bits depending on the data bus size available. This signal is intended for implementing PCI DMA transfers with the Add-On system.              |

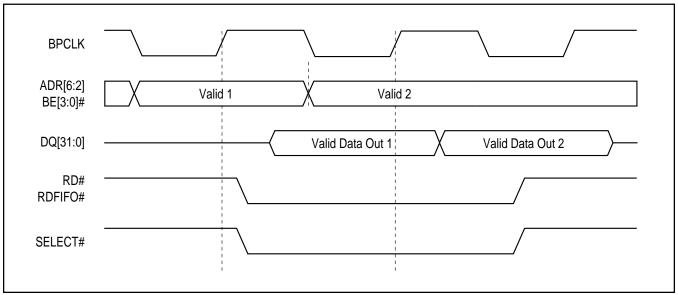

| RDFIFO# | in   | Read FIFO. This signal provides a method to directly read the FIFO without having to generate the SELECT# signal or the ADR[6:2] value of [01000b] to access the FIFO. Access width is either 32 bits or 16 bits, depending on the data bus size defined by the MODE pin. This signal is intended for implementing PCI DMA transfers with the Add-On system. |

| WRFULL  | out  | Write FIFO full. This pin indicates whether the Add-On-to-PCI bus FIFO is able to accept more data. This pin is intended to be used to implement DMA hardware on the Add-On system bus. A logic low output from this pin can be used to represent a DMA write (Add-On to-PCI FIFO) request.                                                                  |

| RDEMPTY | out  | Read FIFO Empty. This pin indicates whether the read FIFO (PCI-to-Add-On FIFO) contains data. This pin is intended to be used by the Add-On system to control DMA transfers from the PCI bus to the Add-On system bus. A logic low from this pin can be used to represent a DMA (PCI-to-Add-On FIFO) request.                                                |

# Pass-Thru Interface Pins

| Signal     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PTATN#     | out  | Pass-Thru Attention. This signal identifies that an active PCI bus cycle has been decoded and data must be read from or written to the Pass-Thru Data Register.                                                                                                                                                                                                                                                                                                                                                                               |

| PTBURST#   | out  | Pass-Thru Burst. This signal identifies PCI bus operations involving the current Pass-Thru cycle as requesting burst access.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PTRDY#     | in   | Pass-Thru Ready. This input indicates when Add-On logic has completed a Pass-Thru cycle and another may be initiated.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PTNUM[1:0] | out  | Pass-Thru Number. These signals identify which of the four base address registers decoded a Pass-Thru bus activity. These bits are only meaningful when signal PTATN# is active. A value of 00 corresponds to Base Address Register 1, a value of 01 for Base Address Register 2, and so on.                                                                                                                                                                                                                                                  |

| PTBE[3:0]# | out  | Pass-Thru Byte Enables. These signals indicate which bytes are requested for a given Pass-Thru operation. They are valid during the presence of signal PTATN# active.                                                                                                                                                                                                                                                                                                                                                                         |

| PTADR#     | in   | Pass-Thru Address. This signal causes the actual Pass-Thru requested address to be presented as outputs on the DQ pins DQ[31:0] for Add-Ons with 32-bit buses, or the low-order 16 bits for Add-Ons with 16-bit buses. It is necessary that all other bus control signals be in their inactive state during the assertion of PTADR#. The purpose of this signal is to provide the direct addressing of external Add-On peripherals through use of the PTNUM[1:0] and the low-order address bits presented on the DQ bus with this pin active. |

| PTWR       | out  | Pass-Thru Write. This signal identifies whether a Pass-Thru operation is a read or write cycle. This signal is valid only when PTATN# is active.                                                                                                                                                                                                                                                                                                                                                                                              |

# **SIGNAL DESCRIPTIONS**

# System Pins

| Signal  | Туре | Description                                                                                                                                                                                                                                         |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSRST# | out  | System Reset. This low active output is a buffered form of the PCI bus reset, RST#. It is not synchronized to any clock within the PCI interface controller. Additionally, this signal can be invoked through software from the PCI host interface. |

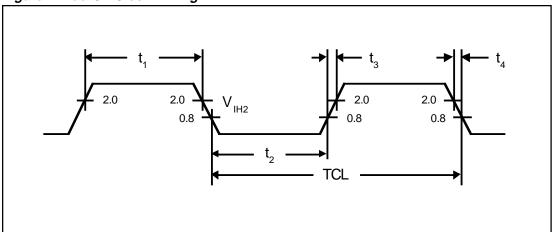

| BPCLK   | out  | Buffered PCI Clock. This output is a buffered form of the PCI bus clock and, as such, has all of the behavioral characteristics of the PCI clock (i.e., DC-to-33 MHz capability).                                                                   |

| IRQ#    | out  | Interrupt. This pin is used to signal the Add-On system that a significant event has occurred as a result of activity within the PCI controller.                                                                                                    |

| RSVD    | in   | Reserved. This pin must be left open at all times.                                                                                                                                                                                                  |

S5935

### **PCI CONFIGURATION REGISTERS**

Each PCI bus device contains a unique 256-byte region called its configuration header space. Portions of this configuration header are mandatory in order for a PCI agent to be in full compliance with the PCI specification. This section describes each of the configuration space fields—its address, default values, initialization options, and bit definitions—and also provides an explanation of its intended usage.

Table 1. Configuration Registers

| Configuration<br>Address Offset                                                                                 | Abbreviation                                                                                        | Register Name                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00h-01h 02h-03h 04h-05h 06h-07h 08h 09h-0Bh 0Ch 0Dh 0Eh 0Fh 10h-27h 28h-2Fh 30h 34h-3Bh 3Ch 3Dh 3Eh 3Fh 40h-FFh | VID DID PCICMD PCISTS RID CLCD CALN LAT HDR BIST BADR0-BADR5 — EXROM — INTLN INTPIN MINGNT MAXLAT — | Vendor Identification Device Identification PCI Command Register PCI Status Register Revision Identification Register Class Code Register Cache Line Size Register Master Latency Timer Header Type Built-in Self-test Base Address Registers (0-5) Reserved Expansion ROM Base Address Reserved Interrupt Line Interrupt Pin Minimum Grant Maximum Latency Not used |

S5935

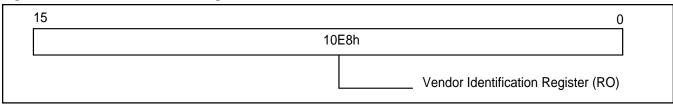

# **VENDOR IDENTIFICATION REGISTER (VID)**

Register Name: Vendor Identification

Address Offset: 00h-01h

Power-up value: 10E8h (AMCC, Applied Micro

Circuits Corp.)

External nvRAM offset Boot-load:

040h-41h

Attribute: Read Only (RO)

16 bits Size:

The VID register contains the vendor identification number. This number is assigned by the PCI Special Interest Group and is intended to uniquely identify any PCI device. Write operations from the PCI interface have no effect on this register. After reset is removed, this field can be boot-loaded from the external non-volatile device (if present and valid) so that other legitimate PCI SIG members can substitute their vendor identification number for this field.

Figure 1. Vendor Identification Register

### Table 2. Vendor Identification Register

| Bit  | Description                                                            |

|------|------------------------------------------------------------------------|

| 15:0 | Vendor Identification Number: This is a 16 bit-value assigned to AMCC. |

### **PCI CONFIGURATION REGISTERS**

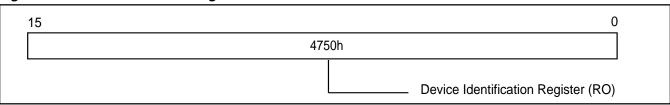

### **DEVICE IDENTIFICATION REGISTER (DID)**

Register Name: Device Identification

Address Offset: 02h-03h

Power-up value: 4750h (ASCII hex for 'GP',

General Purpose)

Boot-load: External nvRAM offset

042h-43h

Attribute: Read Only Size: 16 bits

The DID register contains the vendor-assigned device identification number. This number is generated by AMCC in compliance with the conditions of the PCI specification. Write operations from the PCI interface have no effect on this register. After reset is removed, this field can be boot-loaded from the external non-volatile device (if present and valid) so that other legitimate PCI SIG members can substitute their own device identification number for this field.

Figure 2. Device Identification Register

Table 3. Device Identification Register

| Bit  | Description                                                                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------|

| 15:0 | Device Identification Number: This is a 16-bit value initially assigned by AMCC for applications using the AMCC Vendor ID. |

S5935

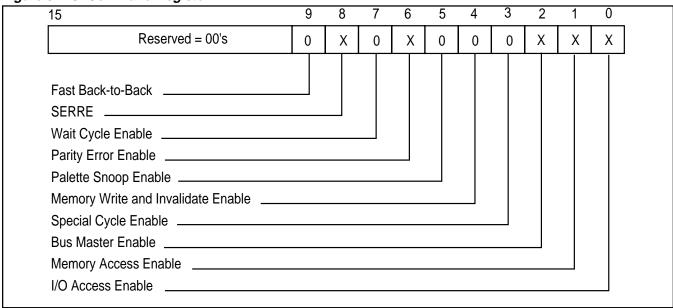

## PCI COMMAND REGISTER (PCICMD)

Register Name: PCI Command

Address Offset: 04h-05h Power-up value: 0000h Boot-load: not used

Attribute: Read/Write (R/W on 6 bits, Read

Only for all others)

Size: 16 bits

This 16-bit register contains the PCI Command. The function of this register is defined by the PCI specification and its implementation is required of all PCI devices. Only six of the ten fields are used by this device; those which are not used are hardwired to 0. The definitions for all fields are provided here for completeness.

Figure 3. PCI Command Register

# **PCI CONFIGURATION REGISTERS**

# Table 4. PCI Command Register

| Bit   | Description                                                                                                                                                                                                                                                                                                                             |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

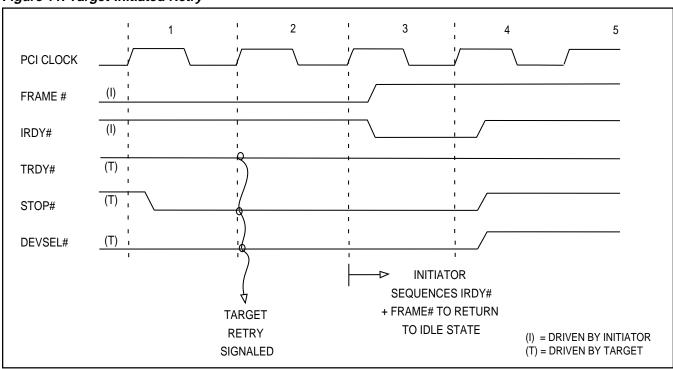

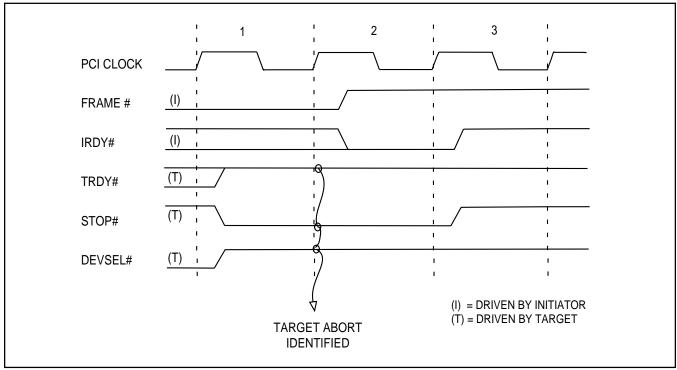

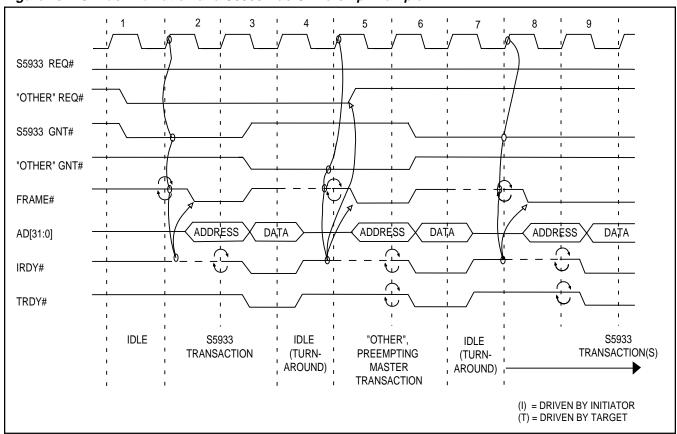

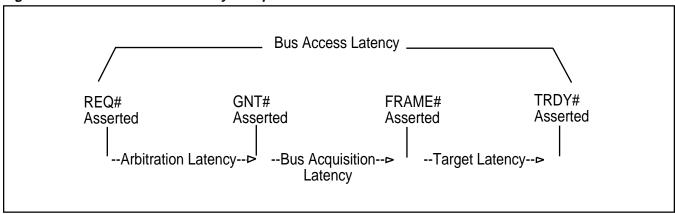

| 15:10 | Reserved. Equals all 0's.                                                                                                                                                                                                                                                                                                               |